欢迎对本期的精彩回答投票,我们将对最精彩的回答送上小小的礼物。以表示对作者无私技术奉献的感谢。

本文中回答均由各位射频从业者们自发讨论回复,回答之中不免有错误疏漏,也欢迎大家批评指正。

01

有关PCB 50欧姆传输线不准的问题讨论

Q: 大佬们,在PCB上要怎么画50欧姆传输线比较准确,我通过计算和仿真确定了传输线的尺寸后进行生产,但是实测结果却和50欧姆相差深远,原因是什么?

A: 设计图片 实测方法呢?

Q: 用的网分仪测s参数,S11只有-5dB左右,就是两个port连两头。

A: PA 哪个工具计算的?叠层结构考虑了?

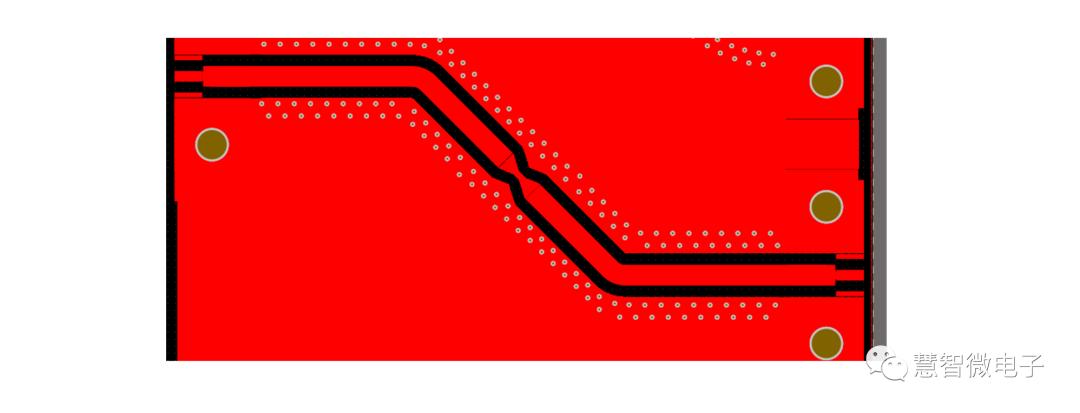

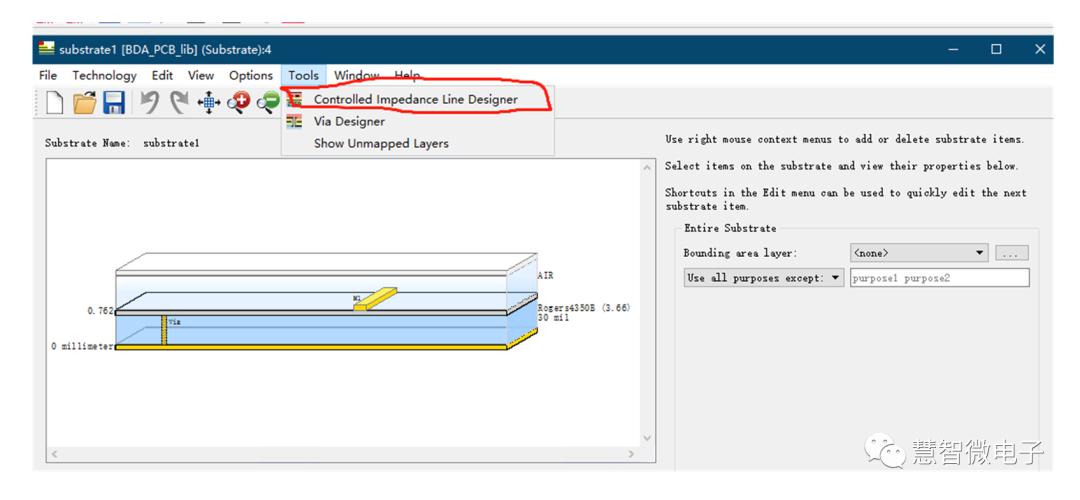

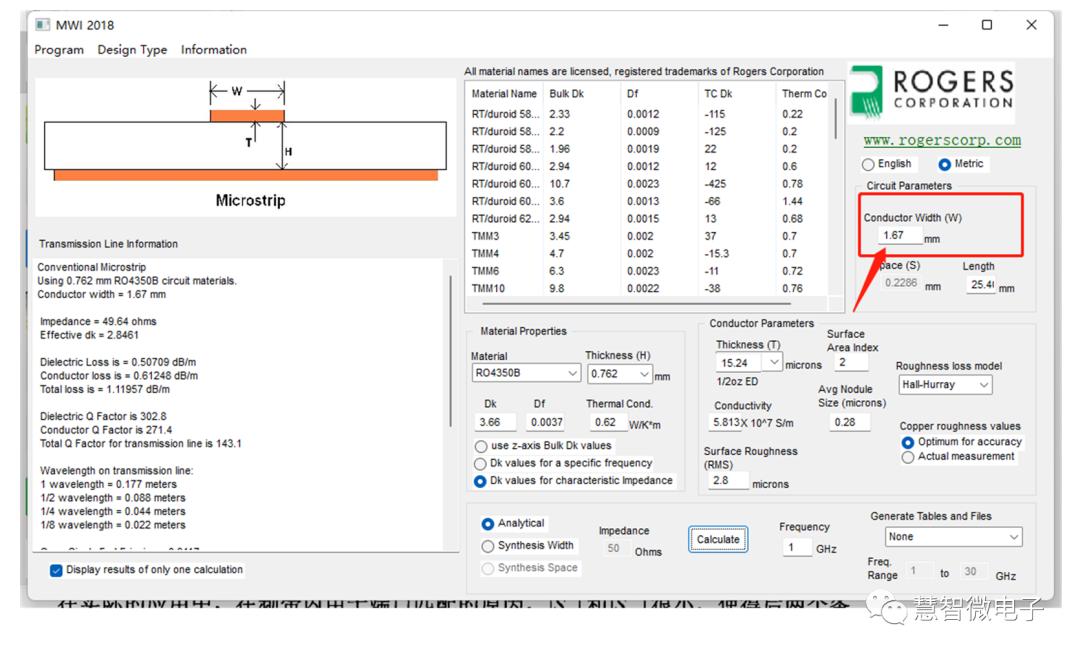

Q: 用这个工具计算的,用的是单层介质板。

A: 中间为何缩线宽了?

Q: 因为中间本来是个芯片,这样做用来去嵌计算。

A: 会不会是因为覆铜距离走线太近了呢?

Q: 但是这个距离我用仿真他就有-15dB左右的S11。

A: 你这个线宽是多少?

Q: 线宽1500u ; 间距750u ;介质rogers4350b 30mil ;铜1oz

A: 30mil 50Ohm 不是直接1670um就完了。

A: 你这个是微带形式,他算的应该是CPWG。

A:两端接插件那也做了匹配设计,会不会实际焊接上去也会偏离。

Q: 两端是根据实际的SMA头设计的,确实没有把阻抗考虑进去。

A: 带SMA头仿真驻波能到多少?

Q: 请问仿真里面怎么把SMA头加进去?

A: 你两头缩窄仅仅是和针一样粗,好焊接是吧?

Q: 是的,只考虑了这点,我想的是尽量和那个针的粗细一样。而且我看这个长度也不长,寻思误差应该只有一点点。

我想问下以各位的经验,50欧姆线仿真的时候驻波是多少,实际做出来又是多少?

A: 仿真-22左右,实际做出来-16 -17,频段是sub 6GHz。

Q: 那我感觉我这个有原理性的错误啊,不然不至于误差这么大。

A: “ 请问仿真里面怎么把SMA头加进去?” 可以用同轴线简单模拟接头带来的影响。

Q: 明白了,感谢老哥。

A : 另外,看一下绿油的影响有没有考虑进来。绿油对特征阻抗会有影响。

Q: 好的,我看一下。谢谢!

02

有关功率管RC等效阻抗的讨论

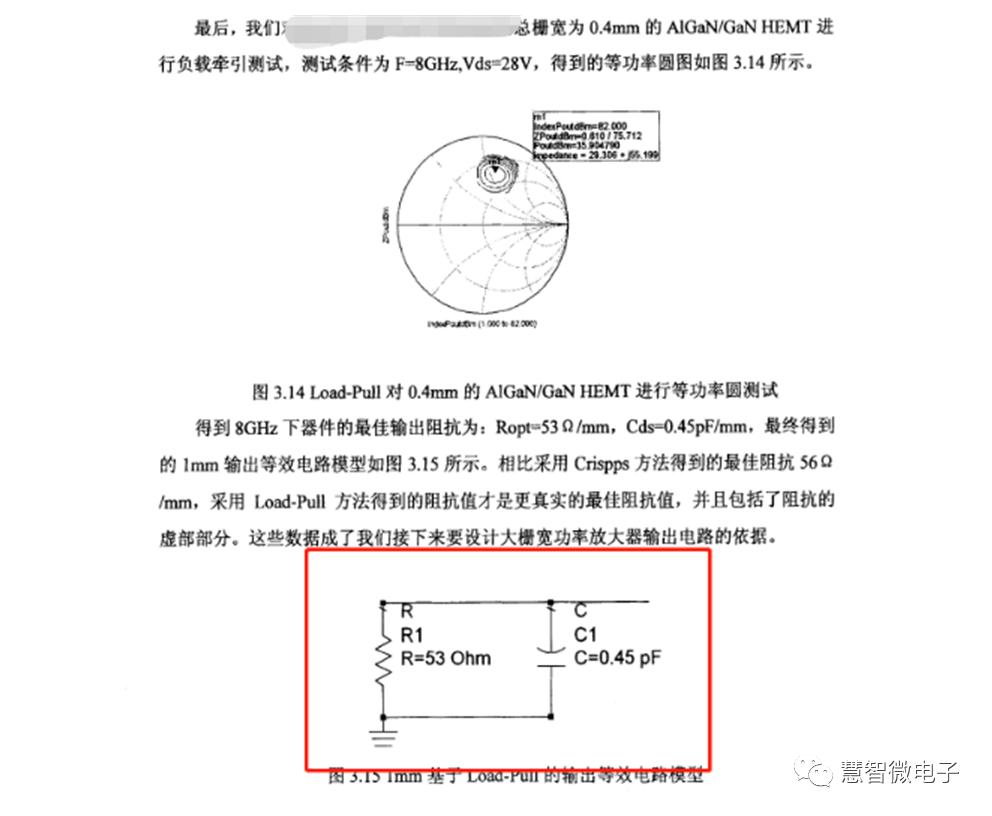

Q: 向各位大佬请教个问题:在做大功率内匹配PA时,设备限制采用Loadpull小管芯,结合Cripps的并联RC的线性模型,算出每mm管芯的RC值作为输出匹配的最佳阻抗。 想请问一下,这个RC的值具体是怎么换算得到呢?

A: 啥文章?

Q: X波段GaN内匹配功率放大器的理论与设计

A: 他这个应该是拟合等效的,就rc并联的阻抗。

Q: load出来是0.4mm的最优阻抗,然后直接缩放为1mm管芯的?

A: 直接缩放,一般都不是很准。

Q: 意思就是等比例估算一下是吧?

A: 是的,这个看工艺,一般S波段以上参考性大一些。L波段单指大了,等效模型不准了。

Q: 好的 谢谢。

03

有关 低温自激的讨论

Q: 为什么 功放自激常见是低温下?

A: 细节参考半导体物理,宏观上增益和跨导成正比,跨导和载流子迁移率有关,迁移率和温度有关,温度的相关性存在一个正的和一个负的二分之三次方的关系。具体的常见的射频半导体,一般是温度低迁移率高,增益高。 温度低,晶格震动小,对载流子散射小,可以这样理解。

Q: 跨导是啥意思啊?

A: 简单理解为电压控制电流的能力。

A: 我的理解mos管正向导通时漏源之间可用一电阻等效,该电阻与温度相关,高温时电阻变大功率减小,低温电阻变小功率升高。

Q: 多谢大佬。

A:另外一个简单的理解方法的是:低温增益高,放大倍数大,容易形成正反馈。

Q: 好的,多谢!

04

有关 供电电路RC结构的讨论

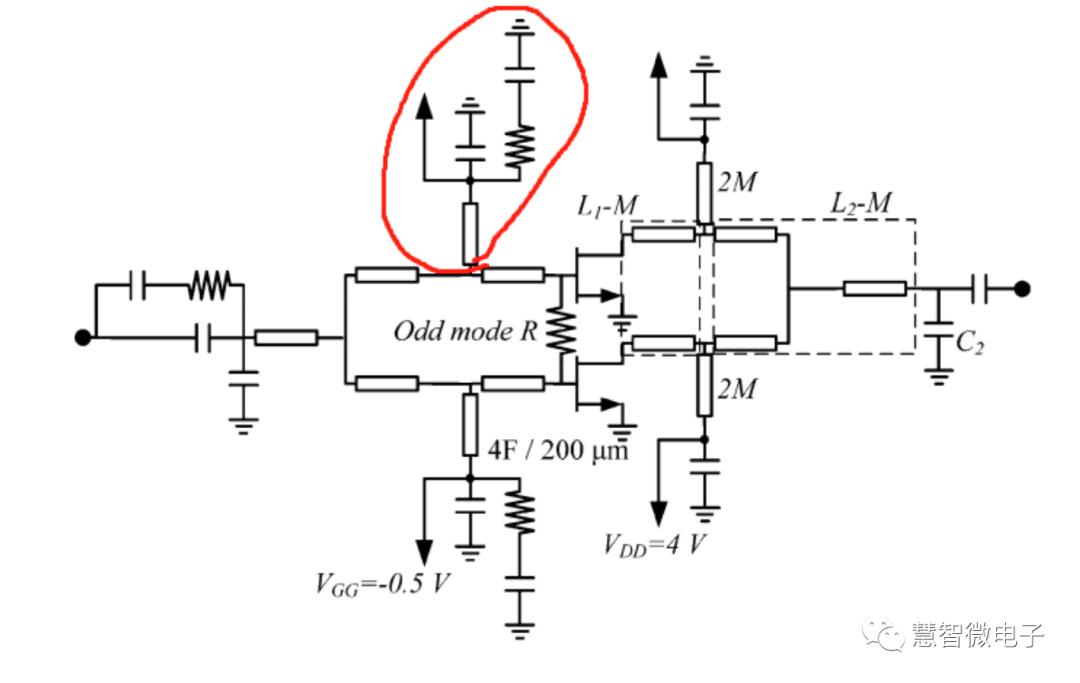

Q: 大佬们,对于这种供电结构有没有啥参考文献推荐下,他那个滤波电容上串个电阻具体是什么原理?

A: 供电的对称臂,一般是用来改善一些线性度指标的啦。

Q: 我以为是用来改善稳定性的,老哥能否细讲

A: 主要不是稳定性的,具体文献我也找不到。

A: 稳定性也能改善,可以改善0频附近的稳定性。

Q: 这玩意儿太难搜了,我找不到相关文献,一看电路,有好多人都用了它,但就是不解释。

A: 找到了共享下,我有空也找找。

A: 就是稳定性,减小电容Q值,防止谐振尖峰。

Q: 请问这个电容是和哪个部分谐振了?

A: 这个电路可以仿真下稳定因子。

A:仿真加上这个RC低频稳定性可以比较高。

Q: 如果是增强稳定性,下面那个供电臂就可以改善,就因为对管么?单管芯也有这种电路应用,我想虽然稳定性是可以改善的,但不是主要的,以前工程上我栅极这里用类似电路可以用来改善IMD3,另外这种对称臂很像漏级的电流对称臂,用来改善视频带宽,优化线性。

Q: 黄色 这部分电路的作用呢?RC?

A: 鲁汶大学Patrick教授对此好像是这么看的,他提出的一些稳定PA的观点里就有这种通过并联高低Q值的电容的方法。

Q: 大佬,这个有什么参考资料吗?

A: 可以去IEEE上搜下Patrick,好像有一篇专门讲稳定性的。

Q: 多谢!

【注:此问题讨论并未收敛,欢迎加入慧智微射频讨论群,继续参与此问题的讨论】

05

有关 HBT实际电流密度的讨论

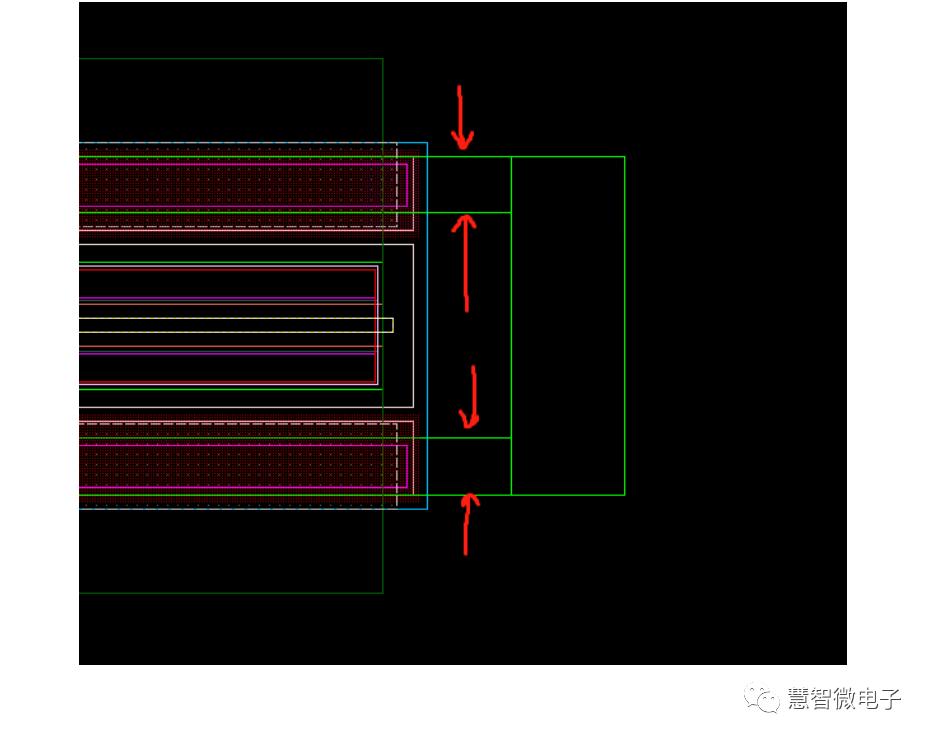

Q: 请教各位专家一下,大家在设计HBT的时候, 有考虑过单个管子这个collector地方的通流么, 如果按照PDK手册来计算, 这个地方M1的电流是4mA/um, 总的电流也就4*8=32mA, 但是实际测试的时候, 电流比这个大一倍 , 实验室也没有看到损坏的情况。

A: 如果是32个管子,你的静态电流就是2A,大佬。

A:这个地方应该不是只有m1吧,是要打孔上上层金属吧。

Q: 32x32差不多1A吧,不过静态电流肯定达不到这么多,是指加上rf的到饱和时的动态电流比较高。

测试的没打孔的,只走m1。

A: 实测电流到多大啊?

A:可以红外看一下温度,一般这个电流能力都标的保守

Q: 实际测试, 按照每个管子均分来计算一下, 每个管子的电流快50了吧.

A: 估计那是个比较安全的值,4mA/um,不一定是超过了就一定坏。

A:超过了不会马上坏,只是寿命降低了而已。

Q: 收到,这个解释合理的, 多谢。

06

有关功放对噪声系数的考虑

Q: 请问各位大哥,功率放大器什么时候需要考量噪声系数呢?

A: 有以下可能:

-GSM产品6step*2dB回退情况下wide-band noise分解时候会考虑影响下行SNR

-功放predriver 的nf会考虑

-还有见过tdd的基站功放有一级没关可能tx噪底抬升可能影响上行、

-还有见过etm2.0a情况下继续大回退功率的对evm的考虑可能涉及功放nf

Q: 多谢!

07

有关 毫米波LNA探针及bonding线寄生电感的讨论

Q: 请问你们设计毫米波频段的LNA,如果用扎针测试方案,会考虑扎针GSG的寄生电感吗?还有单端LNA测试的时候,VDD和VSS的pad如果用绑线,这个寄生电感的影响,大家一般是如何消除的;如果是采用DC扎针,那这个DC针头有多大的寄生电感呢?希望群里大佬能解答一下。

A: 绑线电感一般在设计的时候就把电感给加在原理图里了,可以大概模拟一下实际效果。

Q: 单端电路的绑线电感影响目前是消除不了,如果用DC probe测试,目前也不知道这个寄生电感是多大?不知道群里是否有人用过这个。

单端电路的AVDD和AVSS同时绑线,这个寄生电感一加上,电路就崩了…

A: 耦合器,耦合端可以向输入端耦合吗?即,耦合端输入信号,输入端输出信号。

【注:此问题讨论并未收敛,欢迎加入慧智微射频讨论群,继续参与此问题的讨论】

08

有关 ADS大信号PA仿真的问题

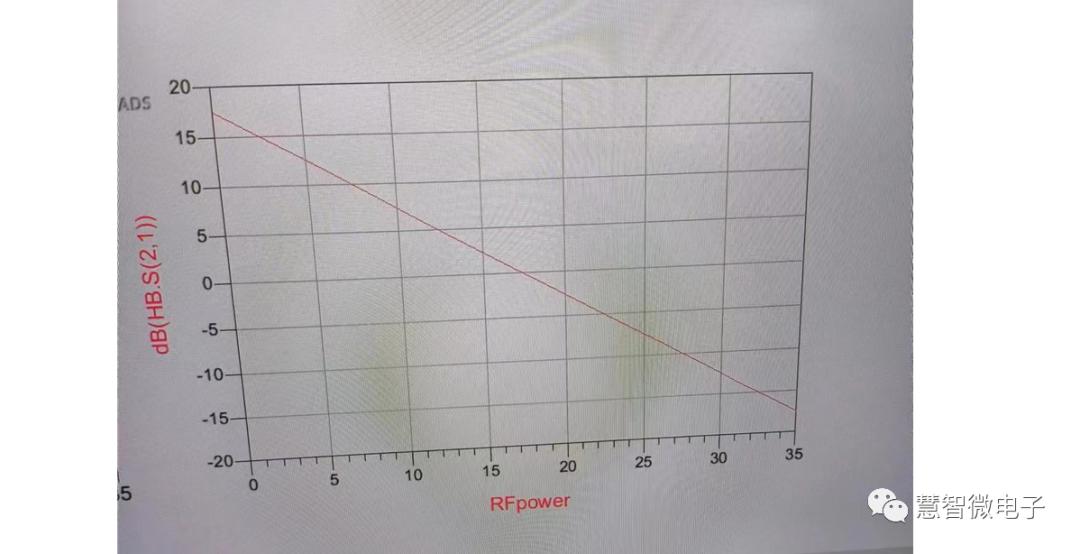

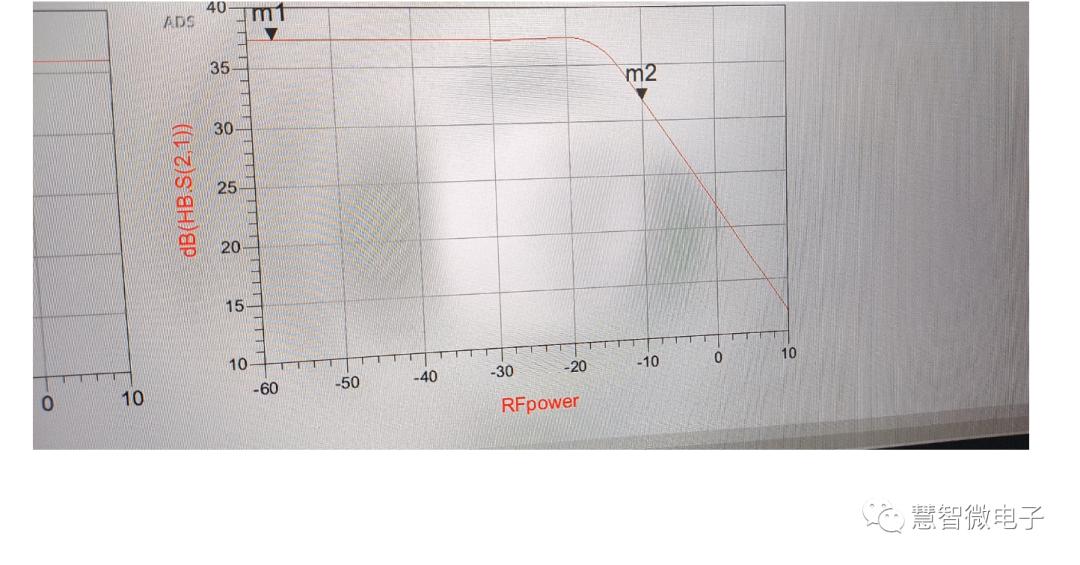

Q: 用ADS仿PA大信号的时候,HB S21是一条斜向下的直线,如图所示。这是哪里出问题了?小信号S参数良好。

A: 是不是激励源设置有问题?

Q: 问题解决了,输入的功率太大了。

A: 正常的跑出来图是什么样的?

Q: 横坐标是输入功率么?

A: 是的。

09

有关LC串联及并联谐振的讨论

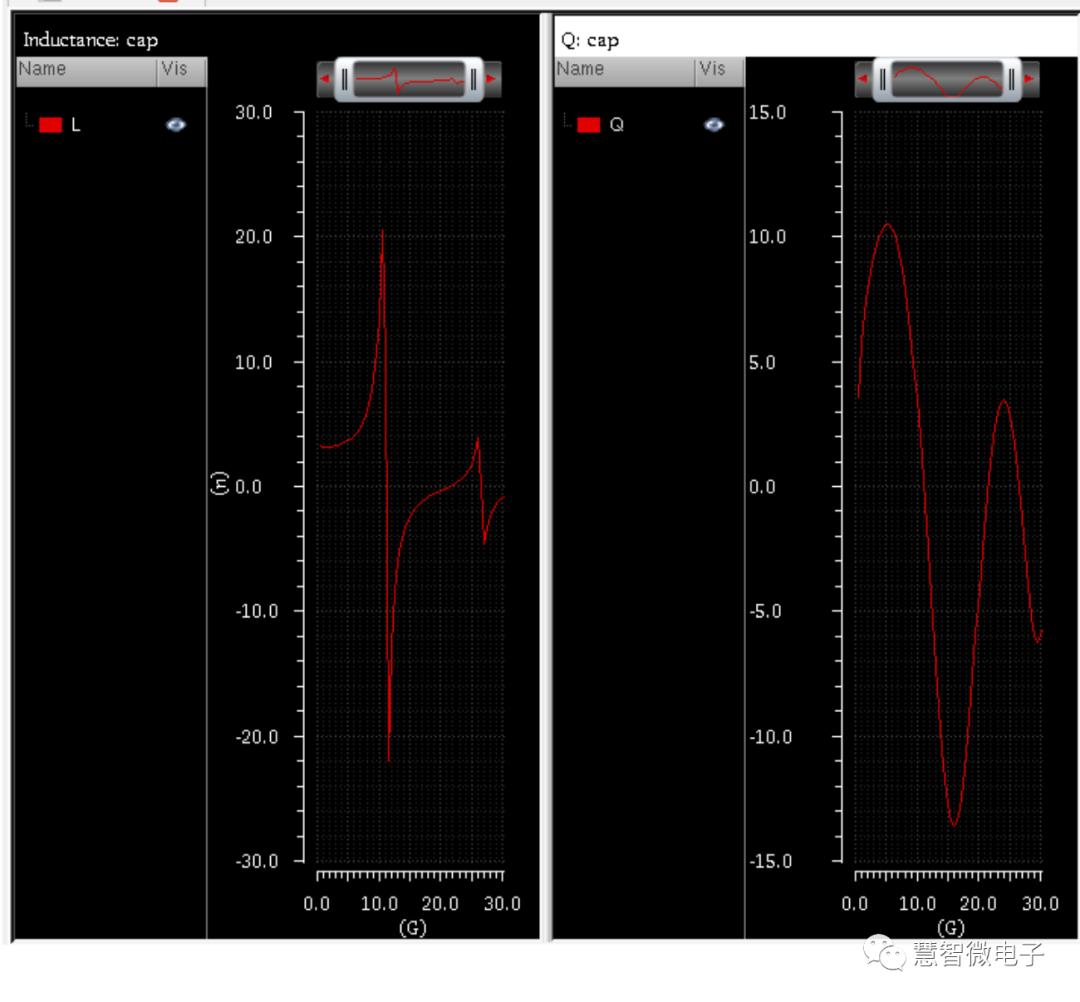

Q: GaAs工艺中,LC串联和并联谐振电路的谐振频率不一样。这是什么原因造成的?

A: 理论上理想情况下是一样的。不过集成电路工艺下可能会有寄生,可以看看是不是寄生电容或电感造成的影响。

Q: 多谢。

10

有关 HFSS仿真中端口设置的讨论

Q: 大家好,请问HFSS仿真中使用波端口时是否需要勾选归一化选项呢?

A: 看想看什么特征阻抗下的S参数,比如想看归一化到50欧的S参数就选上。

Q: 那如果勾选与否之后结果显示有很大的影响,这是否说明端口的阻抗没有匹配到50欧?

A: 是的,端口的特征阻抗和归一化的特征阻抗差别大。

最好勾上,那你跟别人级联起来很容易出问题,其他系统也不可能是严格50欧姆。

Q: 好的,谢谢大家,我尝试一下。

11

有关LNA稳定性设计的讨论

Q: 请问,为了提高LNA的单级稳定性,能在漏级加入电阻吗?

A: 小电阻可以,别太大。有些文章就这样做的。其实你可以选择两级电路,这样稳定性自然就上去了。

A:漏极加不是会影响漏极电压吗?两级电路,单级不稳定的频点最佳匹配点没法得到吧?

Q: 我们利用ADS调整的时候,一般两级电路kf自然就上去了。

A: 我的意思是,两级确实能提高Kf,但是这样级间匹配应该不好做吧!

Q: 哦哦,谢谢大家。

12

有关TX、RX隔离测试的讨论

Q: 请教一个问题,从一个信道的TX,泄漏到另一个信道的RX的强度应该怎么才能测量呢?

A: 从TX通道输入口给信号,在RX输出口测试该频率下的功率。

Q: RX输出口是RX FEM到基带之前的输出么?

A: 是的。

Q: 可是没有接收信号,AGC可能会增益不同。

A: 是要看收发隔离度吗?

Q: 对

A: 两个功率做差值。

Q: 好的,谢谢。

13

有关电路节点电压的讨论

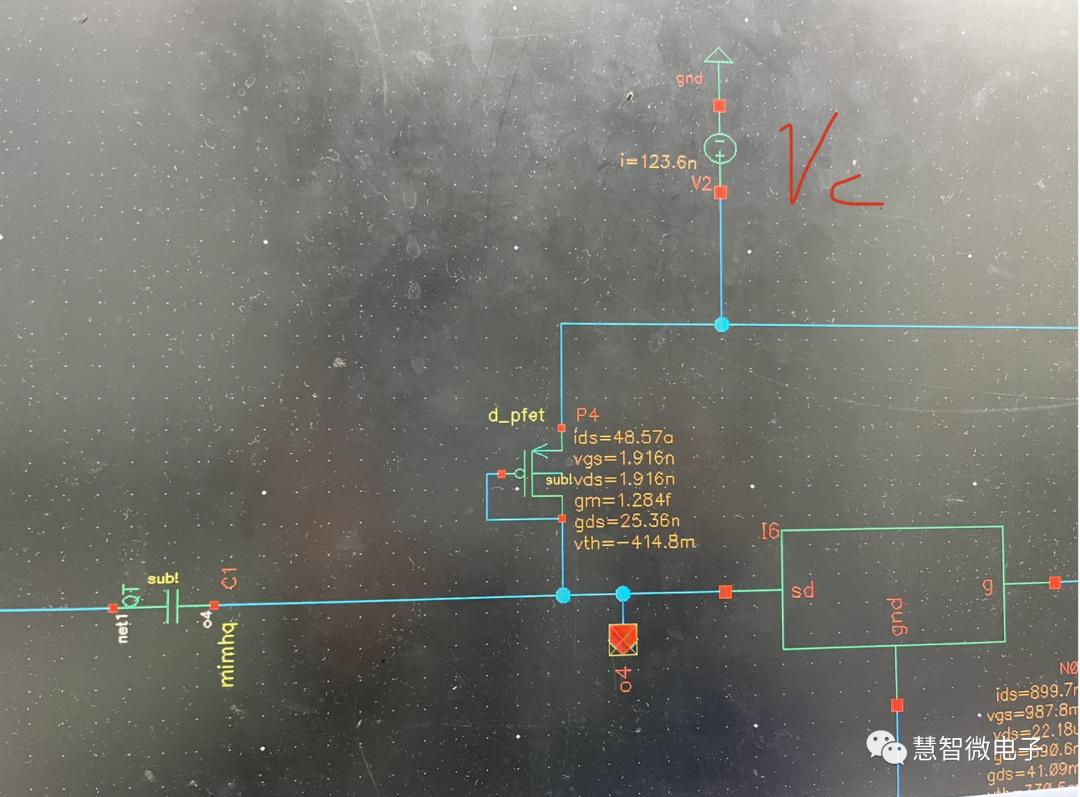

Q: 有朋友知道为什么o4的电压会随着Vc 变化吗?不应该有个电压差吗?o4右边的也是电容。

A: 右边也是电容的话没有直流通路啊,所以pmos必须截止。

Q: 截止的话就可以把电压耦合上去了对吗?

A: 你S端不就是VC变了,你G端就要跟着变,diode连接G和D同电位,所以o4跟着变,你看看那个直流参数VGS是接近于0的。

Q: 为什么S端变了G端会跟着变呢?

A: 管子得截止啊,Vgs不得趋于0么(考虑到亚阈值电流)。

Q: 好嘞,谢谢你!

14

有关交叉耦合VCO设计的讨论

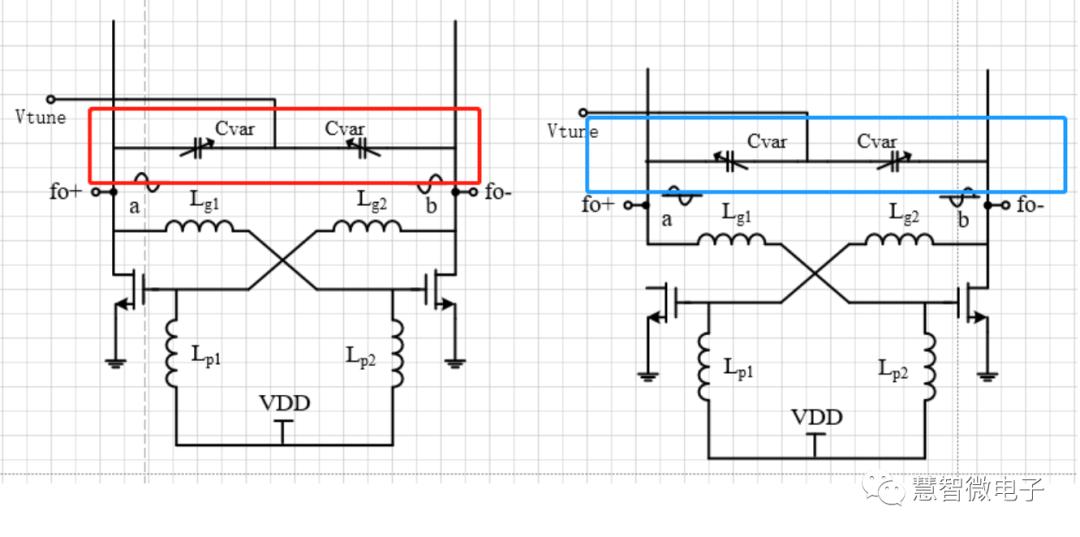

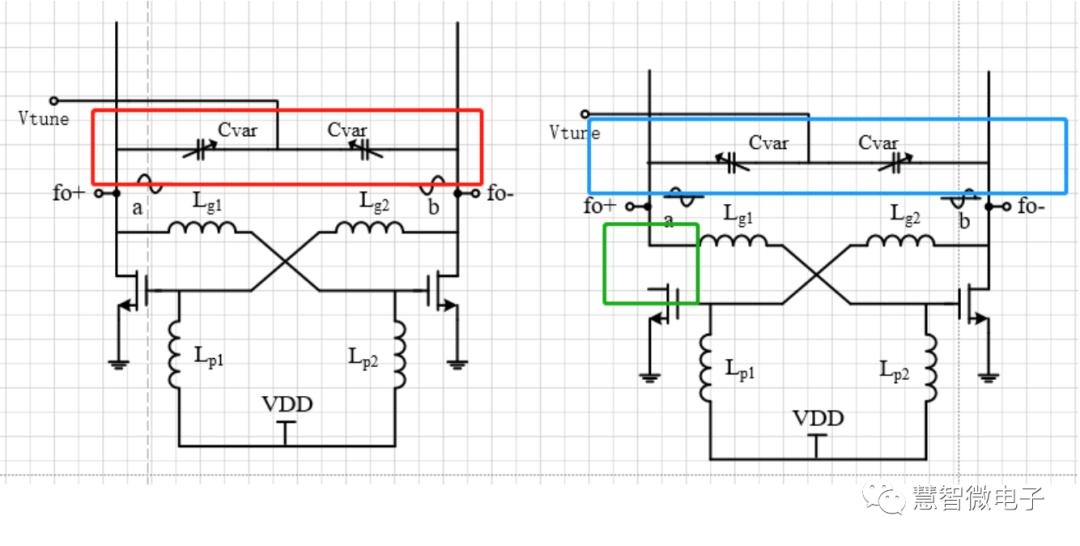

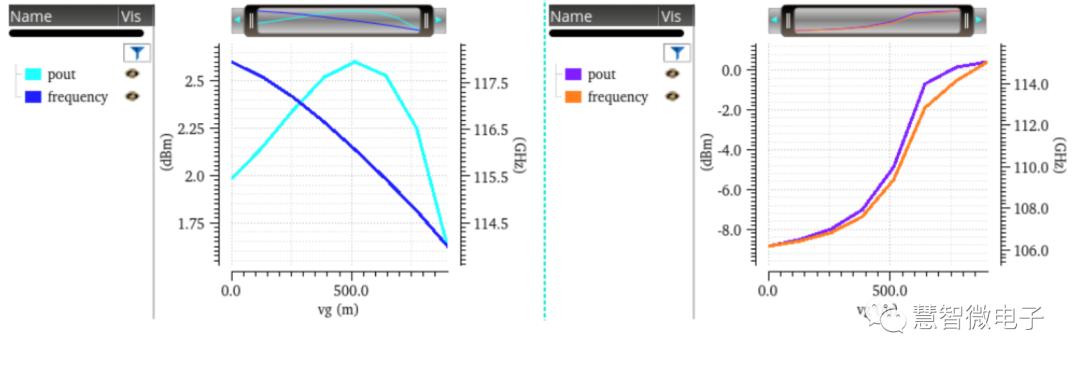

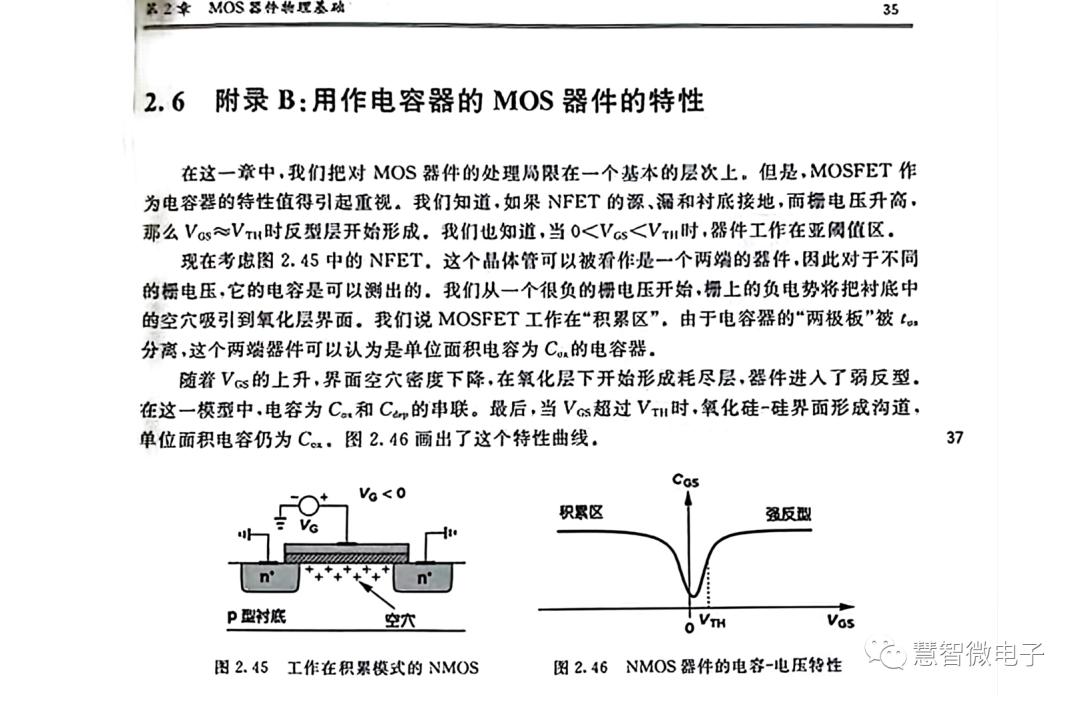

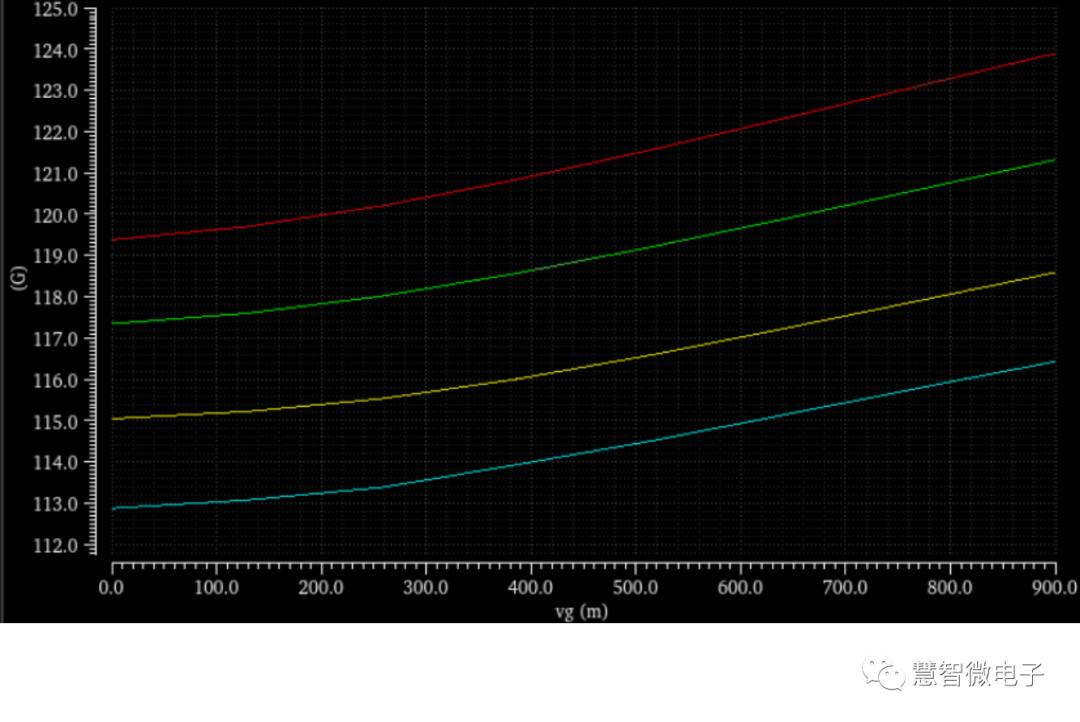

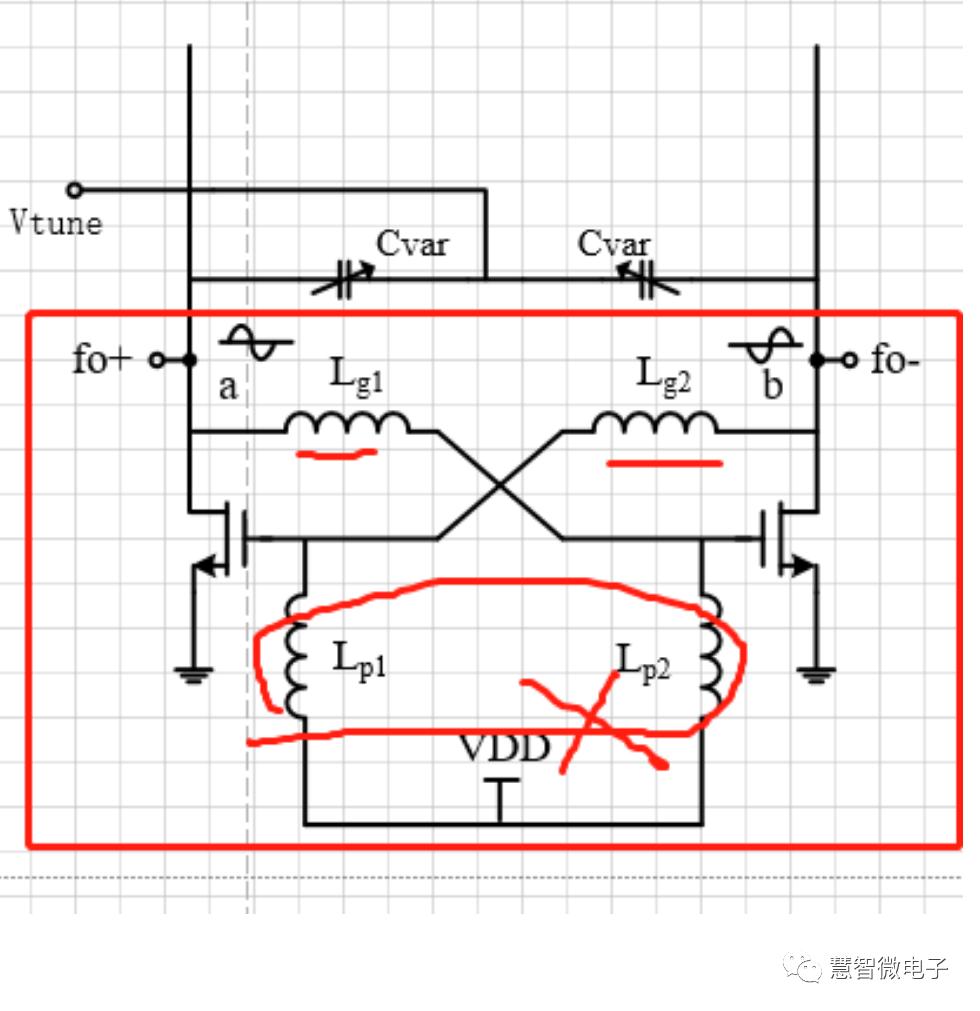

Q: 请问积累型MOS管可变电容应该按照左面接,还是按照右面接呀?

A: 有区别吗?自己搭建一个简单电路仿真对比一下?

Q: 仿真有区别,所以有点困惑

A: 你再仔细看看你的左右图,连接不一样。

Q: 这根线是漏画了,重点是变容管的接法不一样。

A: 电压是不对称的,这个有没有考虑进去。

Q: 嗯嗯,是的。

A: 这确实有点奇怪啊,看看电路原理图。

Q: 问题已经解决了,谢谢各位大佬了。

分享一下:把可变电容调小一点后差别就没那么大了。

A: 我还一个问题:vco不应该采用-2/gm得结构吗?你为啥用的是漏级接电感的形式,区别在哪?我对vco了解不是很多,所以有这个问题。

Q: -2/gm是交叉耦合对产生的负阻, 然后VCO漏极都会连接电感的,与变容管电容构成LC谐振腔。

A: 可是你这里没有形成-1/gm的负阻,会起振吗?

Q: 这部分就会产生交叉耦合对-2/gm。

只不过我做的VCO频率很高,达到了太赫兹,对于一些连接线我用电感进行代替了。

A: 哦哦,原来这样也可以等效为-2/gm的负阻啊,受教了。感谢

15

有关接地通孔感值的仿真

Q: 请问怎么用hfss仿真接地通孔的感值大小呢?

A: 看阻抗的实部虚部。

Q: port口怎么设置呢?

A: 设置成50ohm就可以。

Q: 好的,谢谢。

16

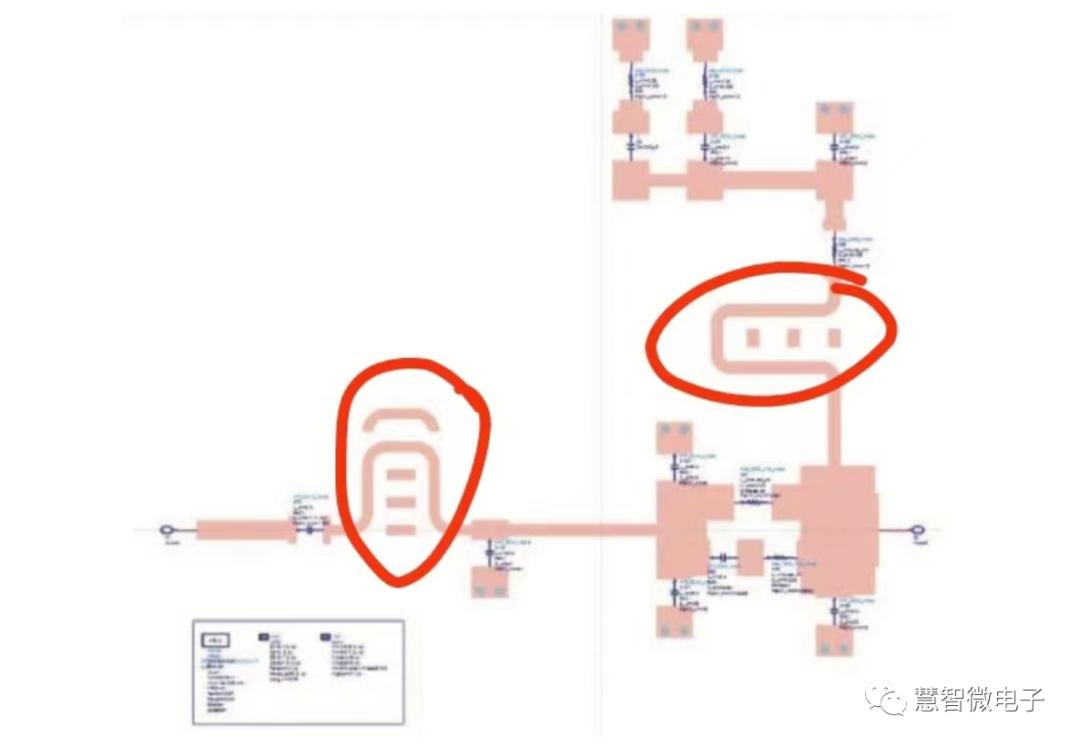

有关射频微波电路Layout的讨论

Q: 请问这种感应回路是怎么用的?

A: 调试用的,不是感应。

Q: 具体怎么操作呢?没看太懂。

A: 用刀把原来的走线割断,再把那一小节连上去,相当于改变了走线长度。

Q: 调相位的?

A: 对。也可以用来贴大面积的铜皮。

Q: 目的是什么呢?

A: 调试啊,万一仿真没那么准么。

Q: 多谢您。

17

有关多个电感串联后谐振点的讨论

Q: 有大佬知道用三个小电感串联来形成一个大电感,这些小电感之间应该做什么处理吗。我直接仿真三个串联的小电感,出现了很多谐振点。

A: 理想情况下肯定不会出现,但是实际情况下由于寄生的原因会出现上面的现象。不知道你出于什么原因用小电感串联成大电感,如果想要减弱这种现象,感觉最好把每个电感的Q值尽可能的调高吧,或许会好一些。

A: 在实际电路中,电感过了谐振点之后会表现为电容,这个电容又和其他电感谐振,所以形成了你看到的多个谐振点的情况,这个现象的出现属于合理现象。

不过要看是否是正常现象,要看谐振点是否符合预期。可以单独仿真每个电路的等效感值 和容值,再计算是否和仿真出来的谐振点对应的起来。如果对应不起来,要看是否还有其他现象。

Q: 多谢。

以上就是本期全部问答内容了,这期 中的问答哪个是您心目中最精彩的呢?欢迎投票