I2C时序延展问题!

-

做硬件设计,总难以避免的要与各种接口打交道,常用的诸如I2C,UART,SPI,网口。每一种类型的接口,在设计上都会有一些自己的要求,但是再简单的东西,也有它独特的地方,今天要讲的是I2C的时序延展。

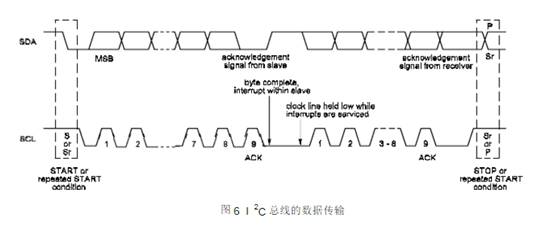

网上搜索一下I2C的资料,基本每一篇文章,每一个文档都会告诉你,I2C线路在硬件上需要做上拉处理,其他的没有特需要求,然后软件上时序跟下图一致即可满足你的应用场景。本来我们也是这样以为的。

最近我们用到一颗TI的芯片,芯片选用I2C作为控制芯片,读取或者写入用户数据,调试的过程中发现用TI的烧录器,每次都能成功,但是更换成我们的主控来做控制,读取寄存器就会出现问题。

首先工程师怀疑硬件问题,因为这个I2C的程序在另外一个程序上做了验证,可以正常控制从设备,于是拆掉其他的I2C设备,只留着这一颗芯片进行测试。发现还是一样的情况。我们拿逻辑分析仪抓波形,发现通信每隔一次都会通信失败一次,IO时序不对应。于是确定是软件逻辑问题。软件工程师验证了TI另外一个型号的芯片,发现数据读取写入都是正常,这个问题就这样陷入了僵局。

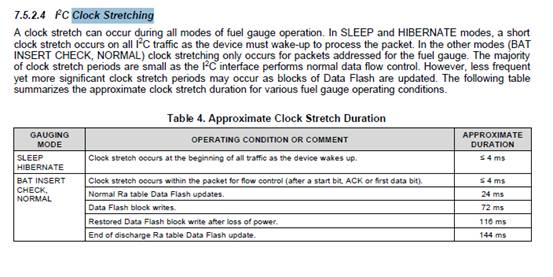

项目工程师决定重新去看一下芯片资料,这一看发现一个没有被大家注意的点:Clock Stretching。规格书是这样描述的:

网上查了一些资料,翻译过来就是在从机休眠的时候,从机会将SCL继续下拉一段时间,这个时候主机要判断SCL是否为高,才能继续传输数据,等从机准备好之后,就会释放SCL的控制,这个时候,就可以开始愉快的通信了。

后面反过来去查询了一下主芯片的设置,发现也有时钟延展的配置,打开这个功能之后,系统就可以正常读写该芯片了。所以下次遇到I2C通信不正常的时候,记得核对一下是不是这个问题导致的。

文|原创:点点

校订:上尉Shonway

更多精彩,专注IT技术,请关注

微信 | 微博:搜"卧龙会IT技术"

------本文由卧龙会自媒体小组成员点点原创,请勿抄袭,转载,转载联系卧龙会进行授权,否则追究法律责任