(报告出品方/作者:民生证券,方竞)

1 长电科技:全球领先的集成电路封测供应商

1.1 全球布局,业务稳步扩张

公司是全球知名的集成电路封装测试企业。公司面向全球提供封装设计、产品 开发及认证,以及从芯片中测、封装到成品测试及出货的全套专业生产服务。通过 高集成度的晶圆级 WLP、2.5D/3D、系统级(SiP)封装技术和高性能的 Flip Chip 和引线互联封装技术,长电科技的产品、服务和技术涵盖了主流集成电路系统应用, 包括网络通讯、移动终端、高性能计算、车载电子、大数据存储、人工智能与物联 网、工业智造等领域。 长电科技的前身是 1972 年成立的江阴晶体管厂,2000 年改制为江苏长电科 技股份有限公司,2003 年成立长电先进,同年在上海证券交易所上市。

作为国内封测龙头企业,长电科技一直以来与国内晶圆代工龙头保持紧密合 作合作,协同发展。股权关系方面,截至 2022 年报,公司第二大股东芯电半导体 (持股比例 12.86%)由中芯国际 100%控股。 在过去的几年内,长电不断通过投资并购、海外设厂,实现了业务规模的持续 壮大和全球化布局: 2015 年,长电科技联合国家集成电路产业投资基金和芯电半导体依次设立了 长电新科、长电新朋和新加坡的 JCET-SC 三个主体,完成了对新加坡星科金朋的 并购,由于星科金朋与多家国际级半导体行业巨头有长期合作关系,公司在并购完 成后一跃成为全球第三、大陆第一的封测企业。 2016 年 5 月,长电科技通过全资子公司长电国际在韩国设立 JCET STATS CHIPPAC KOREA LIMITED(JSCK,长电韩国),整合星科金朋韩国公司的 SiP 业务能力,建设高阶 SiP 产品封装测试项目。 2021 年 6 月,长电宣布完成对 Analog Devices Inc.(ADI)新加坡测试厂 房的收购,并将其业务人员与新加坡子公司完成整合,增强业务能力。

经过二十年多年的发展,长电科技形成全球化的业务布局。公司在中国、韩国 和新加坡设有六大芯片成品制造基地和两大研发中心,在 20 多个国家和地区设有业务机构,可与全球客户进行紧密的技术合作并提供高效的产业链支持。

公司六大生产基地分别位于江阴滨江、江阴城东、滁州、宿迁、新加坡、韩国, 各生产基地分工明确、各具技术特色和竞争优势。两大研发中心分别设立在中国高 密度集成电路国家工程实验室和韩国。

公司业务拥有广泛的地区覆盖,在全球拥有稳定的多元化优质客户群,客户遍 布世界主要地区,涵盖集成电路制造商、无晶圆厂公司及晶圆代工厂,许多客户都 是各自领域的市场领导者。公司在战略性半导体市场所在国家建立了成熟的业务, 并且接近主要的晶圆制造枢纽,能够为客户提供全集成、多工位(multi-site)、端 到端封测服务。

1.2 收入逆势增长,盈利稳健释放

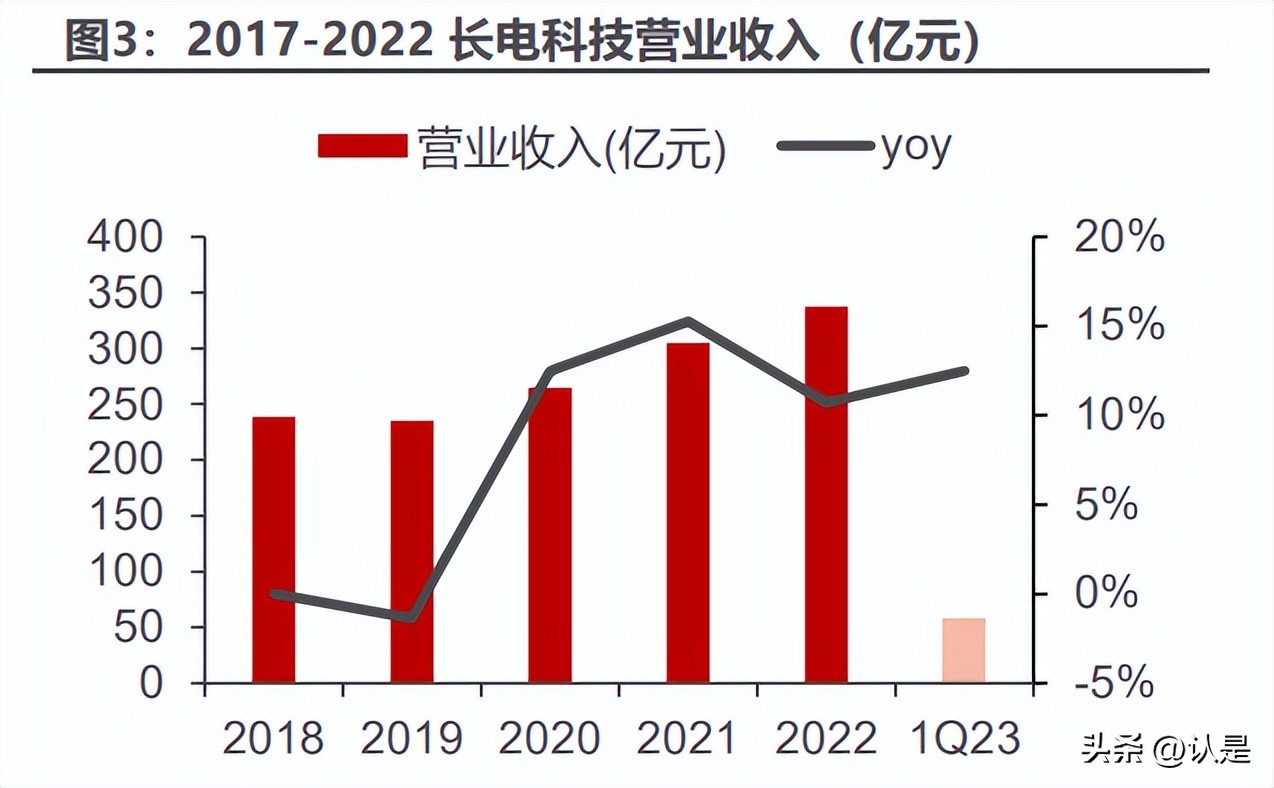

2022 年半导体封测行业景气下行,但公司加快高性能封测领域的研发和客户 产品导入,强化高附加值市场的开拓,优化产品结构和业务比重,现实收入和净利 润逆势增长。2022 年全年,公司实现营收 337.62 亿元,同比增长 10.69%;实现 归母净利润 32.31 亿元,同比增长 9.20%,创历年新高。 2023 年 Q1,受半导体周期性下行影响,公司业绩短期承压,实现归母净利 润 1.10 亿元,同比下滑 87.24%,但收入端仍保持了稳健增速,单季度营收 58.60 亿元,同比增长 12.49%。

利润率和费用率方面,公司在过去数年间通过业务规模增长、运营管理精进, 实现了较好的降费增效和盈利释放。2017-2022 年,公司毛利率从 11.71%提升 至 17.04%,期间费用率从 13.55%下降至 7.47%,2019 年实现扭亏为盈,2022 年实现净利率 9.57%,盈利能力领先国内同业。2023 年 Q1,受行业景气度影响 公司毛利率短期下滑至 11.84%,净利率同步下滑至 1.88%。

从下游市场结构来看,公司下游市场以通信和消费电子为主。2022 年全年, 公司收入结构中通讯电子占比 39.3%、消费电子占比 29.3%、运算电子占比 17.4%、工业及医疗电子占比 9.6%、汽车电子占比 4.4%。 运算电子和汽车电子两大成长性赛道是公司重点发力方向。与 2021 年同期相 比运算电子收入占比增长 4.2 pct,汽车电子收入占比增长 1.8 pct,而消费电子下 降 4.5 pct。

1.3 管理团队技术背景资深

长电科技的多名管理者均为集成电路产业领域的资深专业人士,且具有多年 海外工作经历。其中,首席执行长郑力曾在美国、日本、欧洲和中国的集成电路产 业拥有近 30 年的工作经验,担任过恩智浦全球高级副总裁兼大中华区总裁,瑞萨 电子大中华区 CEO 等高级管理职务。首席技术长李春生在半导体领域拥有 20 多 年的工作经验,曾任 Amkor Technology 首席技术官、全球制造业务执行副总裁 和 Amkor 韩国总裁,拥有韩国专利 38 项,美国专利 21 项。

2 着力布局先进封装技术,强化核心竞争力

2.1 先进封装成为延续摩尔定律的重要路径

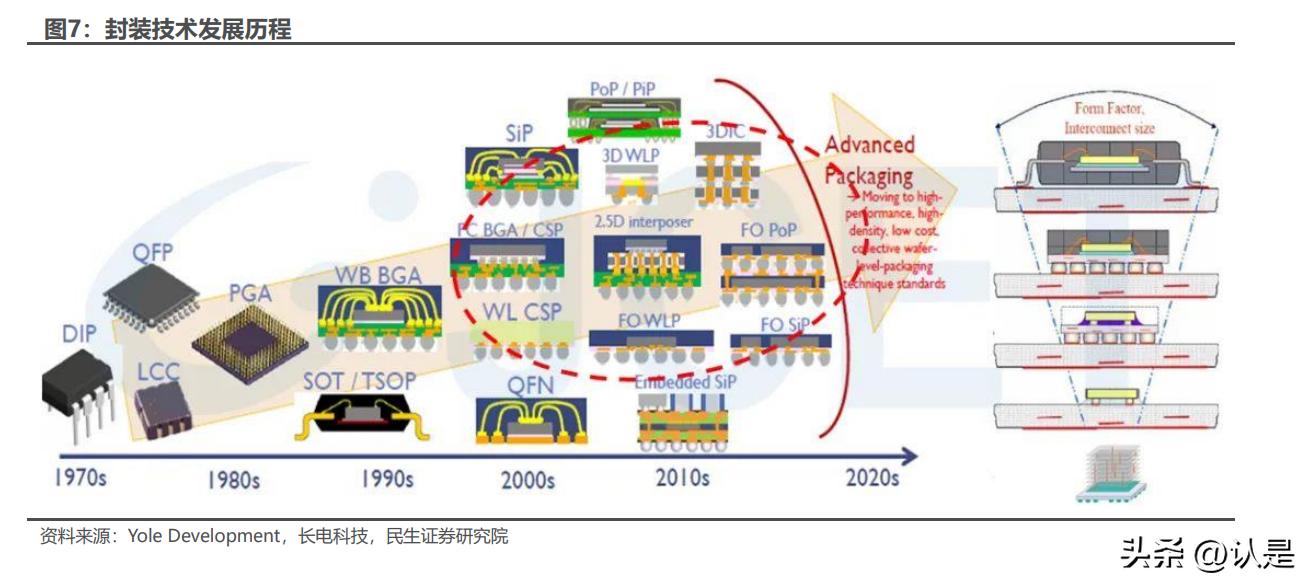

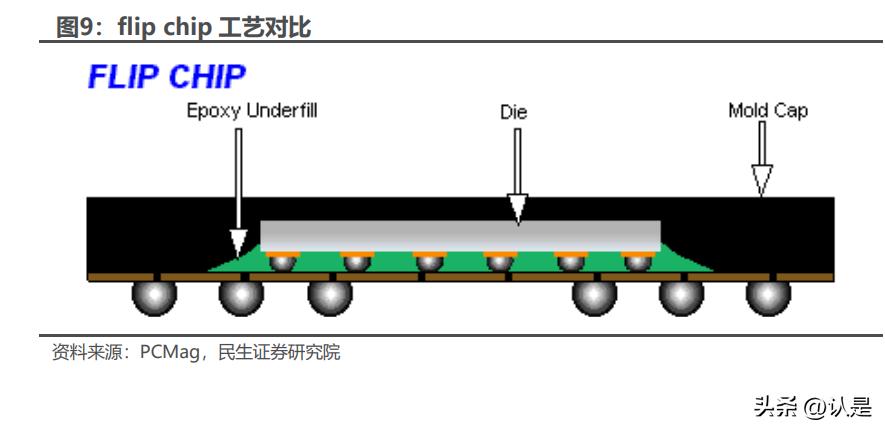

封装为半导体产业核心一环,具有保护芯片、支撑芯片及外形、将芯片的电极 和外界的电路连通、增强导热性能是封装等功能。从传统的引线框架式封装,到先 进的 Fan-Out 等封装形式,封装技术的发展大体上沿着封装面积缩小、密度提升 的路径推进。 传统封装通常采用焊线的方式进行一级互连,而随着芯片的功能进步,引脚数 量逐渐增加,倒装(Flip Chip)逐渐成为高性能芯片的主流工艺。现阶段我们把倒 装成为先进封装,是未来主流发展方向。 而在最尖端的应用中,伴随单颗芯片的面积越来越大,带来的成本大幅提升、 良率大幅下降,先进封装逐渐走向异构集成,即将单颗 SOC 拆成不同功能的小芯 粒(Chiplet),以提升良率,降低成本。Chiplet 技术逐渐成为高算力芯片重点布 局方向。

2.1.1 一级互连:从焊线到倒装

传统封装以引线框架型封装为主,芯片与引线框架通过焊线连接,引线框架的 接脚连接 PCB,主要包括 DIP、SOP、QFP、QFN 等封装形式。 但是,为了适应电路组装密度的进一步提高,引脚间距不断缩小,I/O 数不断 增加,封装体积也不断加大,给电路组装生产带来了许多困难,导致成品率下降和 组装成本的提高。为了容纳更先进芯片的更多的引脚,只有寻找更新的封装,倒装应运而生。

倒装(Flip Chip)工艺,直接在芯片的 I/O pad 上沉积锡球,翻转后焊在封 装基板等表面,锡球取代了原先引线框架工艺中引线的作用。这种封装方式的优势 在于 I/O 引出端分布于整个芯片表面,允许容纳更多的 I/O 接口,封装密度更高, 封装面积可以更接近 die size。广泛应用于高端的数字芯片,如 CPU、GPU、MCU、 NAND、DRAM 等。

2.1.2 二级互连:从通孔直插到 BGA

Wire bond 和倒装两种封装方式是芯片和封装基板之间一级互连的两种不同 技术。而封装基板和 PCB 板之间的二级互连技术亦在持续革新。 传统的引线框架封装,在封装基板与 PCB 之间通常采用通孔直插或引脚贴装。 例如早期的 DIP(Dual In-line Package)封装,又称为双列直插式封装,早在 4004、8086 和 8088 等 CPU 中得到了应用。DIP 封装适合在 PCB 板上实现穿孔 焊接,操作起来比较简单,但用于引脚只能排布在两侧,因此可容纳引脚数有限。 当 CPU 发展到 80286 时代,QFP(Plastic Quad Flat Package,塑料方形扁平 式封装)出现,在整个芯片面积不变的情况下可以容纳更多的引脚,同时信号稳定 性好,能够满足芯片高频率工作的需求。

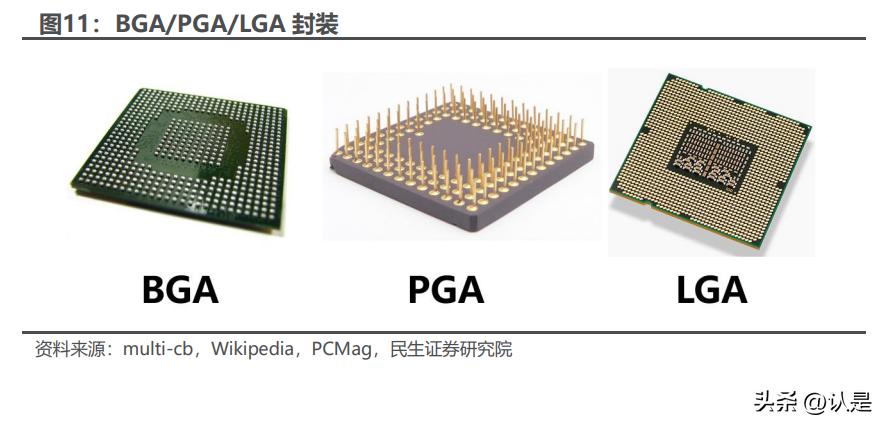

随着芯片 I/O 引脚数急剧增加,功耗也随之增大,为满足发展的需要,在原有 的插装、贴装之外,开拓了新的二级互连方式——球栅阵列封装,简称 BGA(Ball Grid Array Package)。一级互连中的倒装,BGA 封装是在二级互连层面用锡球代 替了引脚,因为锡球遍布整个封装基板的背面,增加了二级互连可容纳的 I/O 数、 缩小了间距,消除 QFP 技术的高引脚数带来的生产成本和可靠性问题。BGA 的出 现,在 GPU(图形处理芯片)、主板芯片组等大规模集成电路的封装领域得到了广 泛的应用。与此同时出现的还有矩形栅格阵列封装(LGA)、插针网格阵列(PGA), LGA 是平面引脚,PGA 则是插针,都是新型的表面贴装技术。

2.1.3 系统级封装

一级互连的 Wire Bond 和 FC 形式均可以用于 BGA/LGA 类封装。若一级互 连采用 Wire Bond,二级互连采用 BGA 形式,则称为 WB-BGA;若一级互连采 用 FC,二级互连采用 LGA,则称为 FC-LGA。 而伴随下游应用对高集成度的需求,系统级封装应运而生。系统级封装工艺将 多枚晶粒(Die)及与其配套的无源电子元器件,根据各自的特点和电气性能要求, 通过不同的封装工艺整合在一颗芯片里,大幅提高了芯片的集成度、电气连接性能, 并近一步缩小芯片尺寸。例如系统级封装可以将处理器、DRAM、闪存、电阻、电 容、连接器、天线等全部安装在统一个衬底上,显著减小封装体积、重量,还可以 降低功耗。

从实现形式上,SIP 封装多以 BGA/LGA 为基础,在一级互连上采用 FC 或 WB 或 FC+WB 混合的形式(称为 Hybrid-BGA/Hybrid-LGA)。混合封装将正装的焊 线芯片和倒装芯片混合封装在一枚芯片里,综合了两类不同封装工艺的技术特点, 属于高端系统级封装产品。

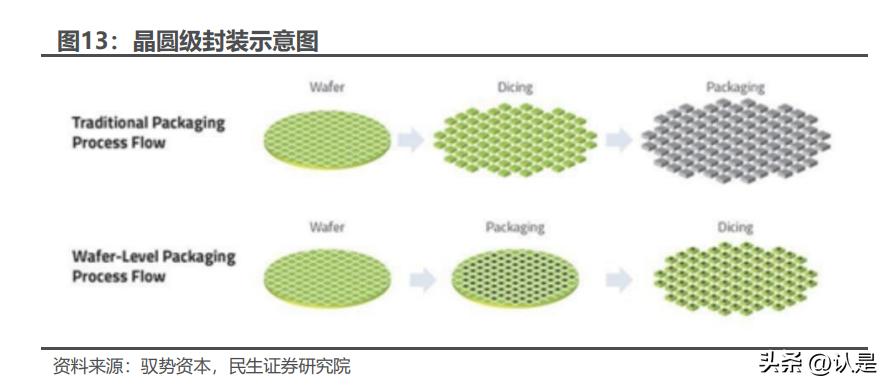

2.1.4 晶圆级封装

在 BGA 类的封装形式中,封装基板起到了重布线的作用,即将芯片的 I/O 口 引出,通过基板上的通线,重新排布成球栅阵列/平面引脚阵列。之后诞生的晶圆 级封装,即在晶圆表面,采用与前道制造类似的铜互连层,完成重布线。 WLP(Wafer Level Package)晶圆级封装在制造流程上,是直接在晶圆/重 构晶圆上进行大部分或全部的封装测试程序,之后再进行切割制成单颗芯片。采用 这种封装技术,不需要引线框架、基板等介质,芯片的封装尺寸减小,批量处理也 使生产成本大幅下降。

WLP 又经历了从 Fan-in WLP(WLCSP)向 Fan-out WLP(FOWLP)的演进。扇 入型 WLP 直接在晶圆上进行封装,封装完成后进行切割,布线均在芯片尺寸内完 成,封装大小和芯片尺寸相同。扇出型 WLP 基于晶圆重构技术,将切割后的各芯 片重新布置到人工载板上,芯片间距离视需求而定,之后再进行晶圆级封装,最后 再切割,布线可在芯片内和芯片外,得到的封装面积一般大于芯片面积,但可提供 的 I/O 数量增加。

晶圆级封装的核心环节是凸块工艺(Bumping),即在晶圆表面制造重布线 层和凸块的环节。Bumping 的雏形是倒装芯片所需的焊球,而倒装芯片一定程度 上替代了引线键合,为此后产生的多种封装形式提供了基础。凸块工艺在产业链中 的位置介于前道晶圆制造和后道封装测试之间,因此被称为中道工序,通过高精密 曝光、离子处理、电镀等设备和材料,基于定制的光掩模,在晶圆上实现重布线, 允许芯片有更高的端口密度,缩短了信号传输路径,减少了信号延迟,具备了更优 良的热传导性及可靠性。

2.1.5 Chiplet

Chiplet 技术属于 SiP 技术的一个新品类,主要用于解决大面积单颗 SOC 良 率日益下降成本上升的问题。Chiplet 工艺将不同工艺节点的小芯粒通过先进封装 技术互联形成大芯片,将大面积芯片成本从晶圆制造环节转嫁到封装环节,提升大 面积芯片良率,日益受到国内外半导体巨头的重视。除了成本和良率上的优势, Chiplet 将 SOC 拆成了模块化的小芯片,实现 IP 复用,加快芯片设计迭代速度。

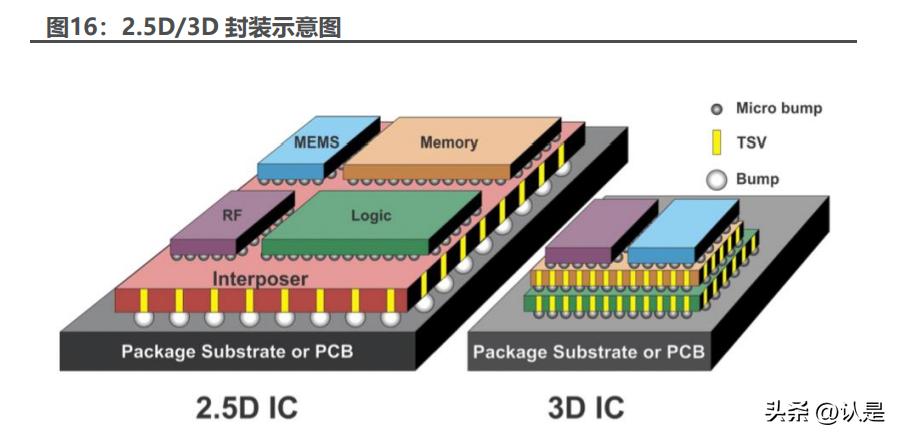

实现形式上,die-to-die 的高速互连是 Chiplet 实现的基础。Chiplet 的小 芯粒可以通过载板或 Interposer 互联,而 Interposer 的材质又分为硅基、有机两 种。若芯片是平铺在封装的衬底上,则称为 2.5D 封装,若是芯片之间堆叠封装, 则称为 3D 封装。

晶圆代工龙头台积电是 Chiplet 工艺的全球领军者。由于 Chiplet 技术涉及芯 片的堆叠,因此台积电将其命名为 3DFabric™技术,旗下拥有 CoWoS、InFO、 SoIC 三种封装工艺,代表当前 Chiplet 技术的三种主流形式。

InFO 方案是以载板为封装衬底,成本相对较低,互联速度相对较慢,无 Interposer。在其变种 InFO_LSI 中在芯片之间互联位置的载板中嵌入了局部的硅 桥,提升两颗芯粒之间的互联速度,苹果 M1 Ultra 采用此种方案。 CoWoS 方案与 InFO 的区别在于加入了 Interposer 的使用,芯粒在 Interposer 上互联,再封装于载板上。硅基 Interposer 方案称为 CoWoS-s,有 机 RDL Interposer 方案称为 CoWoS-R。CoWoS 方案成本较高,互联速率更快, 因此多为算力芯片采用,Nvdia H100 采用此种方案。 SoIC 方案与前两种不同之处在于,前两种方案是在封装环节进行堆叠,而 SoIC 则在封装前就进行了晶圆键合,两片晶圆之间通过 TSV 互联,该方案于 2022 年启动量产。

2022 年 3 月 3 日,AMD、Intel 等半导体巨头宣布共同成立 Chiplet 行业联 盟,目标共同打造 Chiplet 互连标准、推进开放生态,并制定了标准规范 UCIe, 在芯片封装层面确立互联互通的高速接口标准。2022 年 6 月,长电科技加入 UCIe。

2.2 长电科技先进封装赛道实现领先卡位

2.2.1 先进封装空间广阔

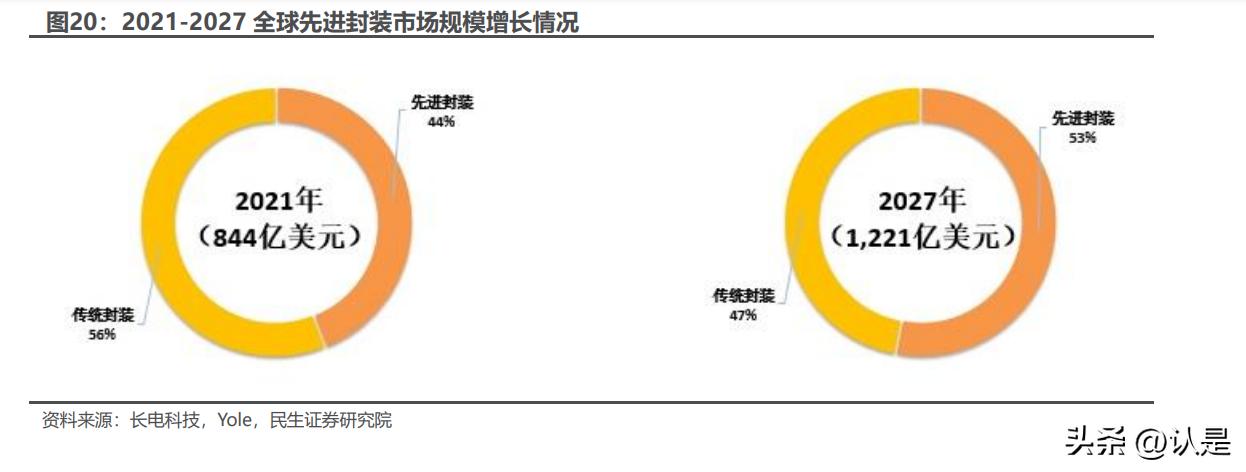

伴随电子产品进一步朝向小型化与多功能的发展,芯片尺寸越来越小,芯片种 类越来越多,其中输出入脚数大幅增加,半导体封测行业对先进封装的市场需求日 益增长,先进封装在整个封装市场的占比逐年提升。 据 Yole 数据,2021 年全球先进封装市场总营收为 374 亿美元,预计先进封 装市场将在2027年达到650亿美元规模,2021-2027年间年化复合增速达9.6%, 将为全球封测市场贡献主要增量。

2.2.2 国产先进封装领军者,前瞻布局异构集成技术

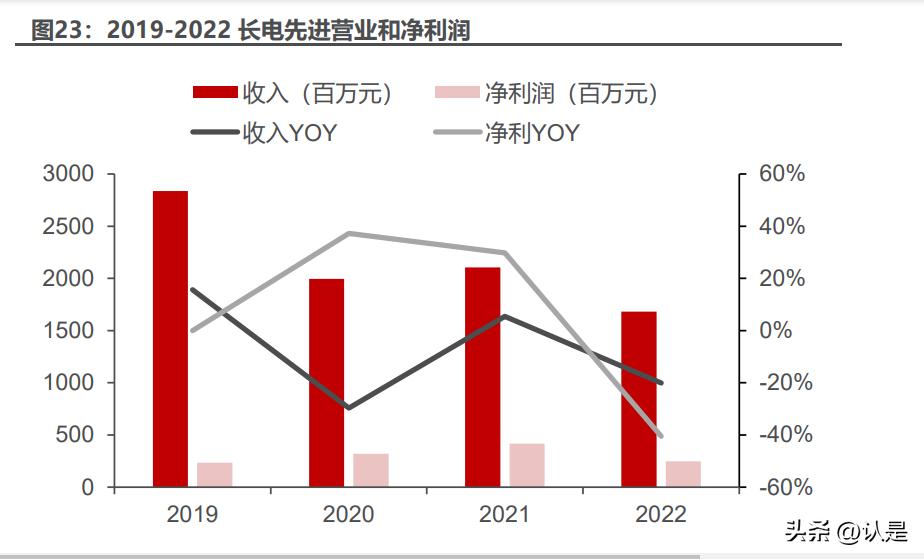

长电科技旗下星科金朋、长电韩国、长电先进在先进封装领域各有建树。 星科金朋拥有行业领先的高端封装技术能力,尤其是在晶圆级扇出型封装 (Fan–Out WLP)和系统级封装(SiP)两个领域,星科金朋所拥有的 eWLB(FanOut 的一种,主要用于高端手机主处理器的封装)和 SiP 在技术上、规模上都处于 全球领先地位。2019-2022 年,星科金朋营收从 10.69 亿美元增长至 19.46 亿美 元,年均复合增速 22.08%。2022 年收入约占长电科技总收入 40%。 长电韩国为长电收购星科金朋之后对其 SIP 业务的再整合所组建,主营高端 SIP 产品封装测试。2019-2022 年,长电韩国营收从 7.48 亿美元增长至 18.49 亿 美元,年均复合增速 35.19%。2022 年收入约占长电科技总收入 38%。 长电先进主营业务为中段 bumping 晶圆级封装。2022 年营收 16.82 亿元, 约占长电科技总收入 5%。

通过各子公司的业务布局,长电广泛覆盖了先进封装的 2.5/3D 集成技术、晶 圆级封装(WLP)与扇出封装技术、系统级封装(SiP)技术、倒装封装技术四大 类主要工艺,其中 2.5/3D 集成技术下游主要覆盖高性能计算市场,扇出型晶圆级 封装技术下游主要覆盖消费电子、IOT 市场,SIP 下游则主要覆盖射频、模拟市场。

在新技术布局方面,公司于 2021 年 7 月正式推出面向 Chiplet(小芯片)的 高密度多维异构集成技术平台 XDFOI™,利用协同设计理念实现了芯片成品集成 与测试一体化,涵盖 2D、2.5D、3D Chiplet 集成技术。 由于 Chiplet 技术的工艺基础是高密度 Fan-Out 封装的芯粒在 Interposer 上的互连,而长电在 Fan-Out 封装领域有长期积累和领先优势,因此公司已率先 Chiplet 技术的稳定量产,在高性能计算、人工智能、5G、汽车电子等领域实现应 用。与客户共同开发了基于高密度 Fan-Out 封装技术的 2.5D FC-BGA 产品,同 时认证通过 TSV 异质键合 3D SoC 的 FC-BGA 产品。 2023 年 1 月,公司宣布实现国际客户 4nm 节点 Chiplet 产品出货。该方案 采用有机 RDL Interposer,可集成放置一颗或多颗逻辑芯片(CPU/GPU 等),以 及 I/O Chiplet 和/或高带宽内存芯片(HBM)等,最大封装面积高达 1500mm2。

3 封测景气复苏可期,龙头强者恒强

3.1 2022 半导体周期下行,景气复苏可期

全球半导体行业具有周期+成长叠加的特征,据 IC Insights 数据,全球半导 体市场规模近 10 年来平均每 4-5 年会经历一轮完整周期,从谷到峰的上行周期通 常是 1~3 年,从峰到谷的下行周期通常 1~2 年,2022-2023 年半导体产业步入 下行周期,IC Insights 预计 2023 年全球市场规模 6040 亿美元,同比下滑 9%, 并有望于 2024 年看到景气回暖。

本轮景气下行的原因主要是电子终端消费市场的疲弱。据 IDC 数据,2022 年 全球智能手机市场出货量 12.1 亿台,同比下降 11.3%;据 Canalys 数据,2022 年全球 PC 出货量为 2.85 亿台,同比下降 16%。受此影响,2022 年手机、PC 等 电子硬件上游的芯片库存持续走高,据 Counterpoint 数据,2022 年 Q4 全球主 要 Foundry 厂的 fabless 客户库存天数达到近 20 年来新高。

受终端需求和下游库存压力影响,2022 年 Q3 以来封测行业增速放缓,以全 球龙头日月光为例,日月光月度营收在 2022 年 6 月增速见顶,并于 11 月步入负 增长。2023 年 3 月,日月光营收 457.75 亿新台币,同比下滑 12%。

但展望 2023 年全年,我们认为有望看到行业景气度触底回暖。正如前文数据 显示,Counterpoint 预计 2023 年 Q2 fabless 芯片设计公司库存天数回到平均 水位附近,IC Insights 亦预计 2024 年全球半导体市场规模将恢复正增长。我们 认为 2023 年 Q2 有望看到封测景气度的底部企稳和下游需求复苏。

3.2 国产封测龙头崛起,公司保持领先地位

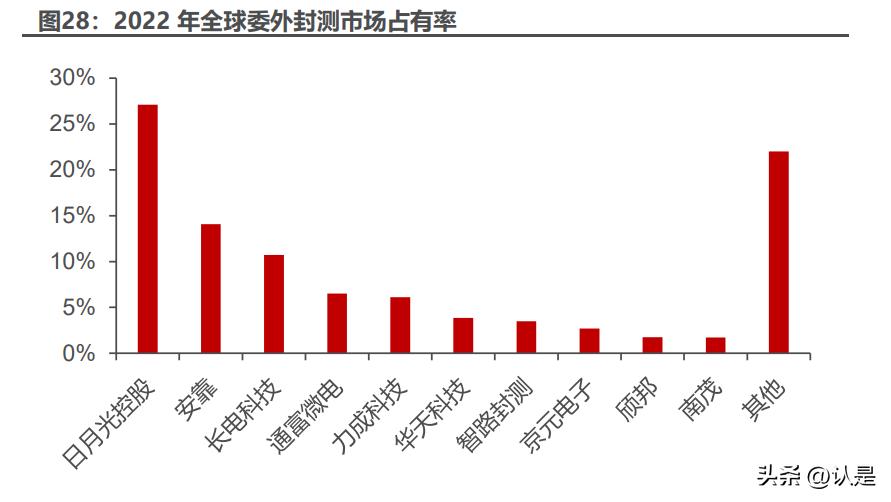

据 Yole 数据,2021 年全球封测行业规模达 844 亿美元。从格局来看,目前 全球封装测试龙头厂商主要集中在亚太地区,并且近年来 Top3 厂商市场占有率超 过了50%,行业集中度较高。据ChipInsights数据,2022年全球委外封测(OSAT) 市场前三分别为日月光(27%)、安靠(14%)、长电科技(11%)。中国台湾地区 前十大厂商占据全球 39.36%市场份额,中国大陆前十大厂商占据全球 24.55%市 场份额。长电作为国内最大的封测龙头,2022 年以 338 亿元的营收体量位居国 内第一,全球第三份额。

3.3 聚焦关键应用领域,重点投入汽车电子及 2.5D Chiplet

长电科技聚焦关键应用领域,在几个主要下游市场如 5G 通信类、高性能计算、 消费类、汽车和工业等重要领域拥有行业领先的半导体先进封装技术,能够为市场 和客户提供量身定制的技术解决方案。 5G 移动终端领域,公司提前布局高密度系统级封装 SiP 技术,配合多个国际 高端客户完成多项 5G 射频模组的开发和量产,产品性能与良率领先于国际竞争对 手,获得客户和市场高度认可,已应用于多款高端 5G 移动终端;此外,公司星科金朋新加坡厂拥有可应用于高性能高像素摄像模组的 CIS 工艺产线,也为公司进 一步在快速增长的摄像模组市场争得更多份额奠定了基础。 车载电子领域,长电科技设有专门的汽车电子事业中心,产品类型已覆盖智能 座舱、智能网联、ADAS、传感器和功率器件等多个应用领域。同时,中国大陆的 厂区已完成 IGBT 封装业务布局,并具备碳化硅(SiC)和氮化镓(GaN)芯片封 装和测试能力,目前已在车用充电桩出货第三代半导体封测产品。

半导体存储市场领域,长电科技的封测服务覆盖 DRAM,Flash 等各种存储 芯片产品。其中,星科金朋厂拥有 20 多年 memory 封装量产经验。16 层 NAND flash 堆叠,35um 超薄芯片制程能力,Hybrid 异型堆叠等,都处于国内行业领先 的地位。 高性能计算领域,长电科技已推出 XDFOI™全系列产品,为全球客户提供业 界领先的超高密度异构集成解决方案。XDFOI™应用场景主要集中在对集成度和算 力有较高要求的 FPGA、CPU、GPU、AI 和 5G 网络芯片等。 AI 人工智能/IoT 物联网领域,长电科技拥有全方位解决方案。公司国内厂区 涵盖了封装行业的大部分通用封装测试类型及部分高端封装类型,江阴厂区可满 足客户从中道封测到系统集成及测试的一站式服务。

2023 年,长电拟计划将主要投资的重点放在汽车电子专业封测基地,2.5D Chiplet,新一代功率器件封装产能规划等未来发展项目,并计划 2023 全年保持 65 亿元的固定资产投资,主要包括:战略投资 20 亿元人民币,产能扩充 18.8 亿 元人民币,研发投入 8.2 亿元人民币,基础设施建设 8 亿元人民币,日常运营 6.3 亿元人民币,工厂自动化与重大技改等 3.7 亿人民币。

4 盈利预测

4.1 盈利预测假设与业务拆分

公司主营业务为芯片封装测试业务,较为单一。考虑到公司在全球各地的业务 布局,以及不同生产基地对应的客户群体在产品形态、市场需求上的差异,我们分 中国大陆业务、海外业务两方面对公司业务进行分拆预测。

中国大陆业务:中国大陆地区业务主要面向国内设计公司,产品形态包括传统 封装、SIP、倒装、晶圆级封装等。受半导体周期影响,2022 年大陆地区业务需求 受损,长电宿迁、长电滁州等子公司收入下滑,国内业务整体收入维持 2.0%的同 比微增。展望 2023,我们认为伴随下游消费复苏,国内业务放缓先于海外,恢复 亦将先于海外。预计 2023-2024 年为底部复苏的上行周期,2023/2024/2025 年 大陆业务收入同比增长 8.0/8.0/6.0%。毛利率方面,同样受周期下行影响,自 2022 年 Q2 开始下滑,我们预计 2023 年有望迎来下游需求回暖和产能利用率提升,同 时伴随国内先进封装需求增长,2024 年以后有望实现盈利进一步提升。预计 2023/2024/2025 年大陆业务毛利率 21.0/24.0/24.0%。

海外业务:公司海外业务主要面向海外龙头设计公司,2022 年在公司总收入 中占比超过 70%,长电韩国、星科金朋两大海外子公司在 2022 年保持了较高的 收入利润增速。考虑到公司海外业务下游以消费电子类大客户为主,下半年通常为 消费电子季节性旺季,因此海外业务在 2023 年 Q1 才表现出放缓趋势,调整时间 相较国内更晚。预计 2023 年海外业务短期承压。但公司在海外子公司持续投入扩 产,且在 2023 年以来逐步拓展国际客户的 Chiplet 封装等高端产品,预计将在 2023 年以后快速放量,未来海外业务仍有望展现比国内业务更高的成长性。预计 2023/2024/2025 年海外业务收入同比增长 0.0/10.0/13.0%。毛利率方面,2023 年短期承压,但伴随大尺寸先进封装的产品逐渐放量和周期回暖,未来盈利能力有 望逐步提升,预计 2023/2024/2025 年毛利率 11.0/14.0/15.0%。

其他业务:与公司主营业务无关,且收入占比不足 1%,对公司盈利不构成显 著影响。预计收入随公司业务规模增长而稳定增长,2023/2024/2025 年同比增 长 3.0/3.0/3.0%,毛利率维持在 50.0%水平。

4.2 费用率预测

销售费用:公司销售费用率较低,且在 2021 年以来稳步降低。预计将保持在 此较低水平,2022-2024 年销售费用率分别为 0.5/0.5/0.5%。 管理费用率:公司 2021 年以来管理费用率随收入增长逐步摊薄,已达到较低 水平,预计未来随收入规模增长平稳下降,2022-2024 年管理费用率分别为 2.7/2.6/2.6%。 研发费用率:公司过去几年研发费用率保持稳定,主要因为持续投入先进封装 的研发。预计伴随公司产品持续迭代升级,在先进封装领域将保持稳定的研发投入, 2022-2024 年研发费用率分别为 3.9/3.9/3.9%。 财务费用:公司财务费用主要来自借款利息,但 2022 年来伴随公司盈利释 放,借款金额逐步下降,预计公司在未来伴随盈利成长将进一步偿还借款,2022- 2024 年财务费用率分别为 0.4/0.3/0.2%。

(本文仅供参考,不代表我们的任何投资建议。如需使用相关信息,请参阅报告原文。)

精选报告来源:【未来智库】。「链接」