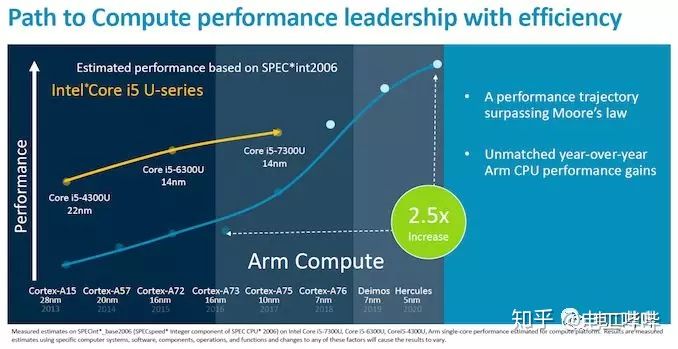

Arm最近补刀华为的事情,令不少业内人士表示不满,详细在此不表了,这个时间点恰逢Arm每年的Techday发布新一代GPU和CPU内核的时间,不管是高喊师夷长技以制夷也好,还是本着技术无国界的态度也罢,让我们一起来关注下今年的新品:Cortex-A77 CPU与Mali-G77 GPU。本文先来分享一下最新采用Deimos架构的Cortex-A77。Arm继续实现了其承诺,并且带来了令人惊喜的浮点性能提升。

本文以下内容翻译自anandtech的Andrei Frumusanu先生,未获得授权,目的在于希望打破国内外的信息流差,如侵立删。

2018年对于Arm自己的中央处理器设计来说是激动人心的一年。去年5月,我们看到了Cortex-A76的发布,最终硅片的产品形态以麒麟980和Snapdragon 855 SoCs的形式出现。A76的表现令我们赞叹,Arm成功实现了其所有的性能、效率和面积的承诺,为2019年的大多数旗舰设备提供了一些出色的SoC和设备。

今年的Techday上正式揭秘了A76的新一代IP——A77。A77在A76的主要架构上推行的直接进化,代表了Arm全新奥斯汀核心家族的第二个实际IP。今天,我们将分析Arm如何推动其新架构的IPC,以及这将如何转化为实际运算性能来满足即将到来的2019年末/2020年初的SoC和设备需求。

Deimos架构的Cortex-A77

Cortex-A77的发布并不令人惊讶,因为Arm继续其传统的每年更新一代CPU和GPU IP的节奏。事实上,今天Arm已经不是第一次谈论A77了:去年8月Arm在发布其2020年性能路线图时透露了中央处理器核心,采用7nm的Deimo(见下图):

代号为“Deimos”的新Cortex-A77从Cortex-A76停止的位置继续前进,并遵循Arm的计划轨迹,即每一代Arm的新奥斯汀CPU家族都能持续提升20-25%的性能CAGR。

在我们介绍新的Cortex-A77之前,我们应该回顾一下A76的性能逐步提升的:

A76无疑是Arm最为成功的授权IP之一,全新的架构与7纳米TSMC工艺节点的重大改进相结合,带来了业内有史以来最大的性能和效率提升。

最终,麒麟980和Snapdragon 855都实现了相比前代产品的重大飞跃。高通公司宣布Snapdragon 855相较上一代搭载A75的处理器性能提升了45%,这是有史以来最大的一代飞跃。

虽然A76表现优异,但并不代表它全无敌手。尽管三星自有的架构与M4缩短了能效差距,Exynos的中央处理器仍然远远落后一代,即使这种差异被今年的工艺节点差异放大(8纳米对7纳米)。Arm的真正竞争对手是苹果的中央处理器设计团队:目前A11和A12仍然保持着领先于Arm大约两代微架构的能效水平。

然而,Arm的优势之一仍然是提供业界最好的PPA。尽管A76的性能与苹果的不太匹配,但它还是以极小的芯片面积实现了卓越的效率。事实上,这是Arm有意识的设计决策,因为电源效率和面积效率是Arm授权厂商的首要任务。

Cortex-A77概述

Cortex-A77是A76的直接架构的继承物,这意味着新的核心基本上与先前的特性保持一致。Arm表示,核心是建立在可以让厂商简单进行SoC升级的设计基础之上。

实际上,这意味着A77与它的前身在体系结构上是一致的,仍然是ARMv8.2的中央处理器核心,它将与动态共享单元(DSU)集群内部的Cortex-A55小中央处理器配对。

作为A76的进化版,A77如预期一样并没有带来很多惊喜,无论是从架构的角度,还是从绝对性能的角度,我们也并不可期望下一代SoC会有大的流程节点改进。

A77预计仍将在大多数客户的7纳米工艺节点上生产,而Arm则宣布与A76类似的3GHz峰值主频。显然,由于频率预计不会有太大变化,这意味着+20%的核心性能提升只能归因于新一代IP架构Deimos带来的变化。

为了实现时钟指令增益,Arm重新设计了微架构,引入了巧妙的新功能,总体上增强了中央处理器的知识产权,从而实现了更宽、更高性能的设计。

Cortex-A77:前端带宽提升

Cortex-A76在架构方面代表了一种全新的设计,Arm从零开始将多年来的CPU设计知识和经验注入其中。这使得该公司能够设计出一个在其微架构方面具有前瞻性思维的新核心。A76原本是Austin家族下两个设计的基准,也就是今天的7nm节点的Cortex-A77以及明年的5nm节点的“Hercules”设计。

A77推出新功能的主要目标是提高架构的IPC。Arm这一代的目标是继续专注于提供业界最好的PPA,这意味着设计师的目标是在保持A76内核卓越能效和面积特性的同时,提高内核性能。

就频率能力而言,新内核保持与A76相同的频率范围,Arm在最佳实现中以3GHz峰值频率为目标。

Arm几乎改动了新架构的每一个部分。从前端开始,我们看到了更高的提取带宽,分支预测器功能增加了一倍,一个新的宏指令高速缓存结构充当L0指令高速缓存,一个解码器宽度增加了50%的中间内核,一个新的整数ALU流水线,以及改进的加载/存储队列和发布功能。

从前端继续深入,分支预测器的一个主要变化是其超前带宽从32B/周期增加到64B/周期。这种增加的原因通常是前端更宽、更有能力,分支预测器的速度需要提高,以便充分跟上向中间核的馈送。Arm指令为32位宽(Thumb为16b),因此这意味着分支预测器每个周期最多可以提取16条指令。这比中间内核中的解码器宽度高(2.6倍),这种不平衡的原因是允许前端在内核中出现分支气泡时尽快赶上。

分支预测器的设计也发生了变化,降低了分支预测失误并提高了其准确性。虽然A76已经具有非常大的分支目标缓冲区容量,有6K个条目,Arm在新一代设计中又增加了33%,达到8K。Arm似乎已经放弃了BTB的等级制度:A76有16个入口的纳BTB和64个入口的微Btb——在A77上,它看起来已经被64个入口的L1·BTB所取代,后者有1个周期的延迟。

新前端的另一个主要特点是引入了宏指令缓存结构。对于熟悉AMD和英特尔x86处理器内核的读者来说,这听起来可能很熟悉,并且类似于那些内核中的操作/操作高速缓存结构,事实上,他们的功能原理确实是类似的。

实际上,新的宏指令高速缓存充当L0指令高速缓存,包含已经解码和融合的指令(宏指令)。在A77的情况下,结构是1.5千个条目大,如果假设宏指令具有与Arm指令相似的32位密度,则相当于大约48KB。

Arm实现高速缓存的特点是它与中间内核深度集成。在指令融合和优化之后,在解码阶段之后(以去耦的方式)填充高速缓存。在高速缓存命中的情况下,前端直接从宏指令高速缓存馈送到中间内核的重命名阶段,减少内核有效流水线深度的周期。这意味着内核的分支预测失误延迟已从11个周期降至10个周期,即使它具有13个周期设计的频率能力(+1解码,+1分支/提取重叠,+1分派/发布重叠)。虽然我们目前没有新内核的直接新数据,但Arm在这方面的数据非常好,因为其他内核的预测失误惩罚明显更糟(三星M3、Zen1、Skylake:大约在16个周期)。

Arm采用1.5K条目缓存大小的理由是,他们的目标是测试套件工作负载命中率达到85%。容量越小,命中率降低得越明显,而使用更大的缓存会降低回报。与64KB的L1高速缓存相比,1.5K的MOP高速缓存的面积约为其一半。

MOP缓存还允许更高的中央处理器的访问带宽。这种结构能够以64B/周期的速度为重命名阶段提供信息,再次明显高于内核的重命名/调度能力,并且这种前端带宽更“胖”的不平衡也允许内核隐藏起来,以快速隐藏分支气泡和管道冲洗。

Arm谈了一点“动态代码优化”:这里核心将重新安排操作,以更好地适应后端流水线。需要注意的是,这里的“动态”并不意味着它实际上是可编程的(类似于英伟达的丹佛代码翻译),逻辑是固定在核心设计上的。

最后到达中间核心,我们看到核心带宽大幅提升。Arm已将解码器宽度从4宽度增加到6宽度。宽度的增加也保证了内核的重新排序缓冲区的增加,从128个条目增加到160个条目。需要注意的是,高通公司的Cortex-A76变体已经出现了这样的变化,尽管我们从未能够确认所采用的确切尺寸。由于Arm仍然负责RTL的改变,如果是完全相同的160入口ROB,我也不会感到惊讶。

同样,只要有MOP缓存命中,中间内核就可以绕过其解码阶段,从而减少一个周期。

Cortex-A77:增加ALUs和更好的访存单元

在讨论了前端和中间核心之后,我们转到Cortex-A77的后端,研究Arm对执行单元和数据管道做了什么样的改变。在内核的整数执行端,我们看到了第二个分支端口的增加,这伴随着前端分支预测器带宽的加倍。

在内核的整数执行端,我们看到了第二个分支端口的增加,这伴随着前端分支预测器带宽的加倍。

我们还看到一个额外的整数ALU上的加法。这个新单元介于简单的单周期算术逻辑单元和现有的复杂算术逻辑单元流水线之间:它自然仍然具有单周期算术逻辑单元操作的能力,但也能够支持更复杂的两周期操作(一些移位组合指令、逻辑指令、移动指令、测试/比较指令)。

Arm表示,新管道的增加带来了惊人的性能提升:随着内核变得越来越宽,后端可能成为瓶颈,这是执行单元需要与内核其余部分一起增长的情况。

最后,现有的执行管道没有看到太多变化。一个延迟改进是复数算术逻辑单元上整数乘法单元的流水线操作,它允许实现2-3次循环乘法,而不是4次循环乘法。

奇怪的是,Arm没有提到Cortex-A77的浮点/ASIMD流水线。在这里,A76的“最先进”设计似乎足以让他们将精力集中在这一代的核心上。

就访存单元而言,我们仍然可以找到两个单元,但是Arm已经在单元中添加了两个额外的专用存储端口,这实际上将问题带宽增加了一倍。实际上,这意味着左/右单元是4宽的,有2个地址生成操作和2个存储数据操作。

发射队列本身再次得到统一,Arm将容量增加了25%,以展示更多的内存级并行性。

为了隐藏系统的内存延迟,数据预取非常重要:通过避免必须等待数据来减少周期可以大大提高性能。如果将Cortex-A76的新预取器(even further)与业内其他CPU进行对比不难发现,A76新预取器的出色表现是Arm的一大优势,它能够处理一些非常复杂的模式。事实上,A76比任何其他测试过的架构都做得好得多,这是一项了不起的成就。

对于A77,Arm改进了预取器,并增加了新的预取引擎来进一步改进这一点。Arm对这里的细节守口如瓶,但是我们被承诺增加模式覆盖率和更好的预取准确性。一个这样的变化被称为“增加的最大距离”,这意味着预取器将在更大的虚拟存储器距离上识别重复的访问模式。

A77中的一个新功能是所谓的“系统感知预取”。在这里,Arm试图解决在不同系统的负载中必须使用单个IP的问题;有些系统可能比其他系统具有更好或更差的内存特性,例如延迟。为了处理内存子系统之间的这种差异,新的预取器将根据当前系统的行为改变行为和攻击性。

我的一个想法是,这可能意味着在某些DVFS条件下一些有趣的性能改进——预取器将根据当前的存储频率改变它们的行为。

这种新系统意识的另一个方面是更多地了解DSU L3缓存的缓存压力。在其他中央处理器核心高度活跃的情况下,核心的预取器会看到这一点,并缩小其攻击性,以避免不必要地抖动共享缓存,从而提高整体系统性能。

性能目标:IPC提高20-35%

在Cortex-A77我们看到了一些有趣的架构变化,有望提高性能。现在的问题是,目标性能提升最终会体现在哪里?

在公布的性能改进方面,Arm选择继续使用SPEC2006,2017,GeekBench4和LMBench内存带宽。我们的重点将放在SPEC2006上,因为它仍然是移动设备中最相关的基准。

在SPECint2006标准下,A77承诺将达到23%的IPC提升,而SPECfp2006实际上显示性能增加了35%。整数工作负载增加23%或多或少符合我们对CPU内核的预期,但是我必须承认,浮点工作负载增加30-35%是相当令人惊讶的,特别是因为我们没有看到内核的浮点执行单元有任何显著变化。这里的一个解释是,SPEC的FP测试套件比整数套件内存更密集,而Cortex-A77的各种架构改进在这些工作负载中会更加明显。

去年,我在两个频率点上对A76进行了性能和效率预测,最终我非常接近麒麟980和Snapdragon 855的性能结果。对于Cortex-A77,事情应该更容易预测,因为我们不会在下一代7nm SoC中看到主要的过程节点变化。

基于已发布的理论上的2.6GHz的A77的IPC的提升,和麒麟980的当前结果,我可以大致推断出其性能。需要注意的是,虽然Arm今年再次谈到A77的3GHz的目标频率,但我不期望供应商在即将到来的SoC中能达到这个频率,预测仍将是2.6GHz的主频。

就性能而言,整数套件会有一些实质性的改进,但是浮点结果要有趣得多。如果正确的话,A77将会超过苹果A11的FP性能,并带来相当大的一代的推动,尽管我们并不期待大的流程节点改进。值得注意的是,A77将不得不在今年晚些时候与苹果的A13以及三星的下一代M5内核竞争。

Arm承诺A77的能效将与目前的A76 SoC保持一致。因此,在最高性能时,两个CPU内核将使用相同的能量来完成一组工作负载。然而,A77性能的提高有一个缺点:功耗增加,与性能指标的提高成线性关系。后一种增加的功耗似乎会达到这样的水平,即在移动SoC中,以峰值频率运行两个以上的内核会更成问题。幸运的是,大多数供应商已经从4个全速大内核发展到只有一到两个高功率大内核的2+2或3+1设计。

值得注意的是,尽管我们在这里谈论的是大内核,A77据说只比A76大17%,仍然比竞争对手的下一个最佳架构小得多。

写在最后

总的来说,今天Cortex-A77的发布没有我们去年在A76上看到的变化大,也没有今天Arm新Valhall GPU架构和G77 IP的发布大。

然而,Arm通过A77成功实现的是继续执行他们的路线图,这在竞争环境中极其重要。A76实现了Arm的所有承诺,最终成为性能极高的核心,同时保持惊人的效率,并在竞争中拥有明显的密度优势。在这方面,Arm的主要客户仍然非常注重在其产品中拥有最好的PPA,Arm在这方面也有所贡献。

A77最大的惊喜是它的浮点性能提升了30-35%,比我对内核的预期要高得多,在移动领域,网页浏览是一个致命的应用,恰好浮点运算量很大,所以我期待着未来A77的SoC将会如何表现。

但是,即使在整数工作负载中,20-25%的IPC增益也绝对是惊人的改进,我们相信Arm能够保持A76的能效。功率会略有上升,但我认为业界已经表明,今天的移动设备至少可以处理两个更高功率的内核,因此未来的SoC应该继续采用大+中+小的CPU配置。

供应商即将推出的A77处理器预计仍为7nm——高通和海思是两个明显的领先客户,他们将采用该核心,我预计其时间框架与上一代芯片组相似。目前,Arm正在兑现他们承诺的每年20-25%的CAGR,我们相信这种情况会持续到可预见的未来几代。