我国今年28纳米光刻机已经量产,预计2021年交付用户。

光刻机是中国芯片的最大痛点,国产光刻机承载了太多的希望。

CPU由数十亿个微型晶体管组成,这些晶体管是通过开关来进行计算。

把通电看成是1,不通电是0,CPU就靠0和1的组合进行工作

●这个工作需要能量,晶体管越小,所需的功率就越小。

“10nm”是英特尔2019年第四季度首次亮相的新制造工艺,“7nm”是2019年台积电的工艺。

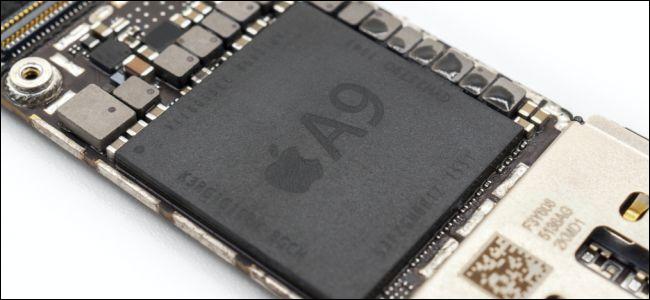

我们知道英特尔是制造电脑芯片的,台积电主要是制造的手机芯片,虽然手机芯片的集成电路数量高于电脑芯片,但是大家都知道电脑芯片的处理能力远远超过手机。

●决定CPU或者是GPU性能的最核心指标并不是晶体管的尺寸,而是逻辑电路的构架。

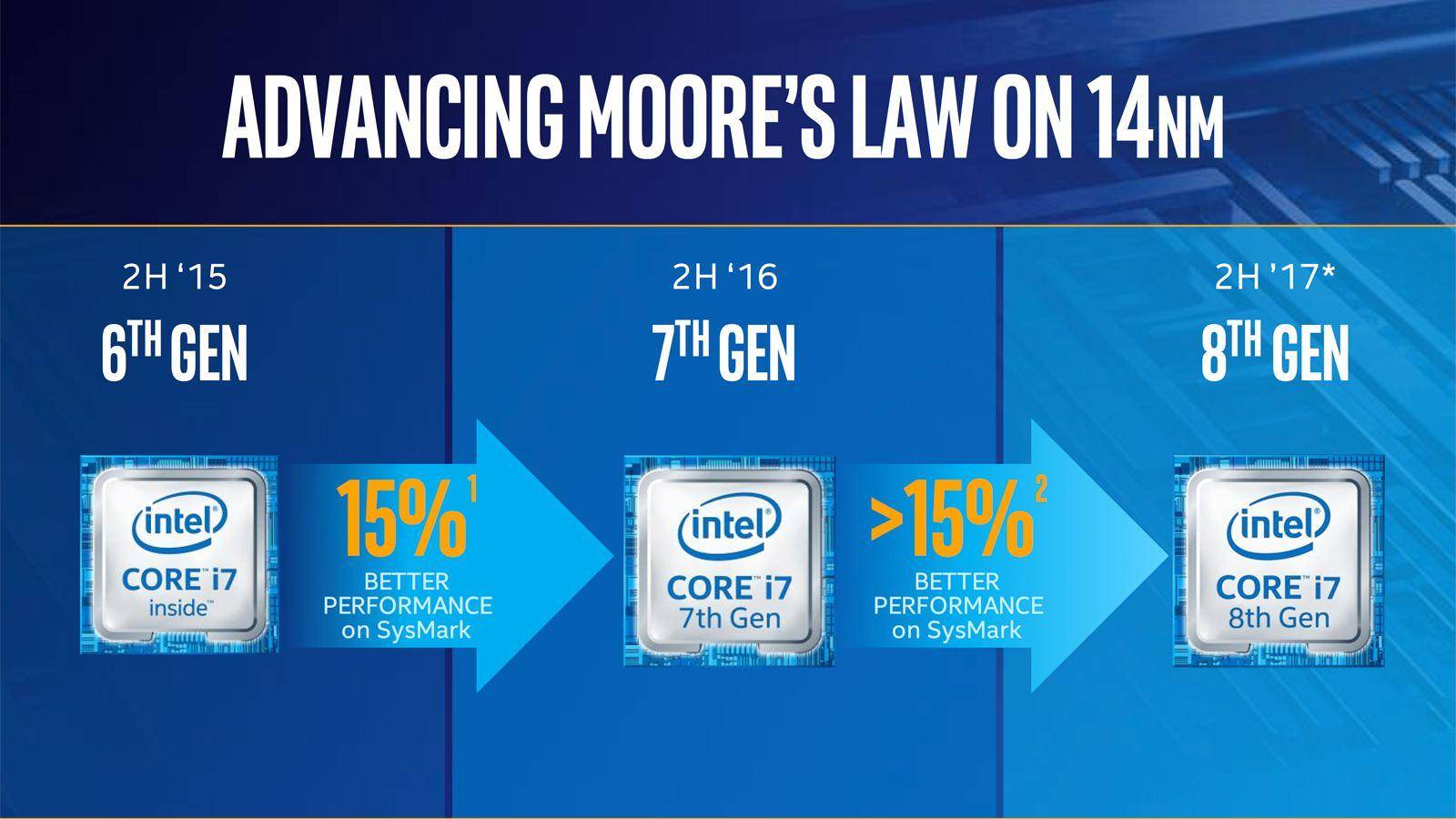

摩尔定律(Moore's Law)问世已经几十年了,即芯片上的晶体管数量每年翻一番,而成本却减半。这一观点在相当长的一段时间内是正确的,但最近一直在放缓。

早在上世纪90年代末和21世纪初,晶体管的尺寸每两年就缩小一半,导致了定期的大规模改进。但进一步的缩小变得更为困难。

●自2014年以来,英特尔公司的晶体管尺寸一直维持在14纳米

而且,就算过了六年,今年英特尔发布最新10代酷睿处理器,仍然使用了14纳米的工艺。

尺寸每缩小一半,单位面积上集成的电路可以增加4倍。但是这种增加是要以制造缺陷为代价的。

尺寸越小,制造出来的CPU或者是GPU上面的缺陷越多。为了弥补这些缺陷,就不得不设计出更多的备用线路。GPU上晶体管数量已经迈过50亿数量级,向100亿迈进,性能仍然达不到桌面电脑CPU的水平。

华为麒麟980里面的晶体管数量已经达到69个亿,而酷睿i7 4960X晶体管数量只有18.6亿。

基本上7纳米的工艺都集中在手机等移动数字设备激烈竞争的行业。

●手持设备受到尺寸严格限制。

所以不断的追求更小的晶体管尺寸,就能集成更多的电路。更小的尺寸也意味着耗电量更低。

虽然桌面电脑暂时不受CPU耗电量的限制,但是高性能的桌面电脑或者是服务器越来越大的发热量意味着冷却越来越困难

●个人电脑的液冷机箱动辄上万元。

CPU越强大,就必须在性能、可靠性、功率和散热量以及冷却系统之间做出妥协。

如果用28纳米甚至65纳米来制造七纳米工艺的GPU、CPU,得到的集成电路尺寸更大,耗电量也会更大,但是性能会更加稳定。

这就好像完全一模一样的建筑采用更厚实的材料来制造,当然是性能更好。

如果把7纳米的工艺放大到28纳米,相当于把电路里面的铜线面积加粗,抗干扰性能会更强。

*用军**集成电路为了追求稳定性和抗干扰性一般都会使用28纳米以上工艺。

为了追求极高的信号噪声比,HiFi发烧友用的功放里面都是用最粗的电路。

●晶体管都不够大,要换成真空管,这就是所谓的胆机。

但是这样做的代价就是贵。

如果是一次性投入的设备贵一点就贵一点,但是某些产品是消耗性的,那么成本就很有意义。

●卖方展示马克沁机枪的射击,一分钟内打断一颗大树。

最后一挺机枪也没买回来。一分钟600发*弹子**,大清消耗不起。

即便是英特尔这样的个人电脑CPU顶级生产商,在笔记本电脑的芯片上仍然是有压力的。因为更小制程的芯片可以在相同功率下获得性能提升,或者用更小功率获得相同的性能。这也意味着在相同性能的情况下,电池寿命更长。

集成电路现在做的越来越小,很大程度上是源自市场竞争的压力。

10大类需要用到大规模集成电路的设备:

服务器、个人电脑、工业应用、可编程逻辑设备、数字信号处理设备、移动通信终端、核心网络设备、半导体储存器、可编程逻辑设备、数字信号处理设备。

●我国占有率最高的是移动通信终端中的两个细分设备,应用处理器占了18%,通信处理器占了22%。

再接下来是半导体存储器,NOR FLASH、Image Processor都只占据了5%的规模。

在单晶硅尺寸固定的情况下,把制程做得更小,可以利用硅片的边缘。集成电路面积小1/2,硅片的利用率会提高20%左右。

7纳米的芯片用28纳米来做,在不计成本的情况下满足*用军**可以,民用市场除非国家强推。

●据说远程火箭炮上炮弹一枚就要几十万元,相当于一辆宝马车的价格。

如果与水平相当的对手打成消耗战,最后比谁的*弹子**数量多,最后肯定是要比拼成本的,这也是一种国家之间的竞争压力。

中国的成本优势只是暂时人工成本有一定的领先,高科技产品的成本控制上,中国不一定能占优。

●马斯克Star link最终建成需要4.2万颗卫星,成本控制是核心和关键。

而卫星设备恰恰是集成电路占了最重要的成本。

硅原子有大小,晶体管尺寸不可能无限小下去,现在已经基本上接近于工程制造极限,进展很艰难。14纳米是一个稳定的节点,这个节点代替7纳米还是可行的。

凡事都有条件,不谈条件,只谈是与非是不对的。半导体芯片的尺寸问题也是如此。