电路设计中,有时会用到一些以前编写过的设计代码。通常比较好的做法是把这些类似的可以复用的模块,独立定做成一个IP块以备以后需求。同时这样做也有很多好处,能够将你的设计制作成BlackBox,也就是网表文件,这样别人看不到你的设计但是可以调用你的模块。这里面主要用到了Black Box的设计。很多时候会使用公司的或者第三方公司的IP核,如何把自己的HDL代码变成可使用的IP呢?详细的参考信息如下。

(1)什么是BlackBox:一个大的设计中可以用到一系列网表文件作为输入的一部分,而并不使用全部的HDL文件。当综合这个大设计时,综合器不需要知道这个网表文件是怎样实现的,只需要知道它的输入输出接口就可以了。这样的网表就称为BlackBox(黑盒子),因为我们不需要看到它的内部情况。通常付费IP都会以BlackBox的形式出现。

(2)如何使用BlackBox:BlackBox网表可以是EDIF或NGC文件。每个BlackBox网表都需要一个与之相对应的HDL文件来注明它的端口。这个HDL只说明BlackBox的端口信息,而不提供具体的实现信息。这个只提供端口信息的HDL文件称为Wrapper。Wrapper的名字通常需要与BlackBox网表的名字相同。在ISE工程中,使用BlackBox时只需要将它的Wrapper添加到工程中,然后像普通的模块一样在其上层声明和例化就可以使用。BlackBox网表文件可以放在ISE工程目录中,也可以放在其他任意文件夹内。当不放在ISE工程目录中时,需要在Translate属性中将Macro Search Path指向这个目录。多个目录使用"|"分割。

(3)如何制作BlackBox:BlackBox只是普通网表而已,XST的综合结果就可以直接作为BlackBox使用。通常BlackBox外部还会连接其他逻辑,所以BlackBox中一般不插入IOBUF。在XST属性中去除Insert IO Buffer的选项。

(1)一般收费的IP都是只提供网表供使用,自然对设计的保密是一大好处。

(2)IP都是验证好的模块,提供给外界接口,自然使用方便也是一大特点。

(3)以网表形式提供可以保持IP的内部时序完整性(保存设计),类似于partition和smartguide。

案例:生成IP核的具体操作过程

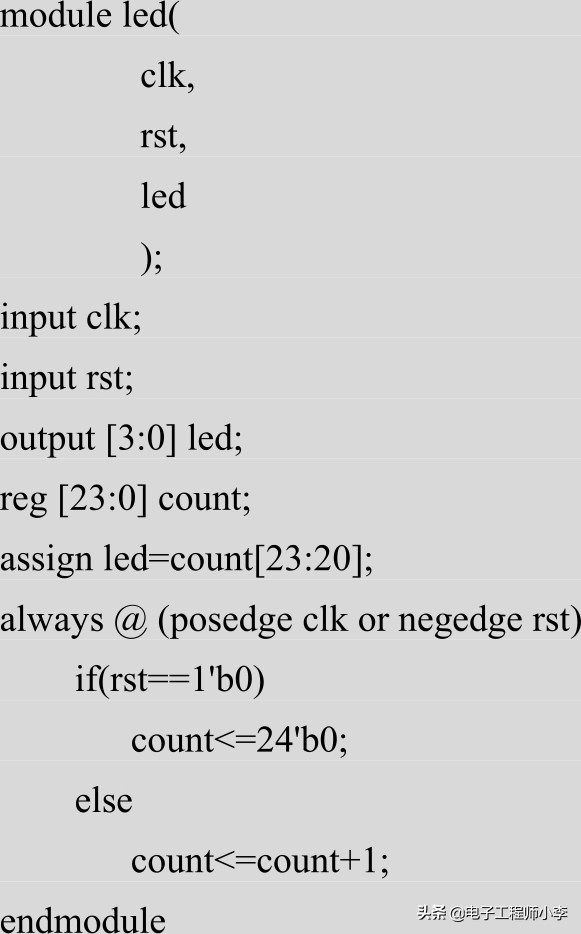

第1步:像通常建立工程设计一样,先编写一个模块,如下是显示发光二极管灯亮程序:

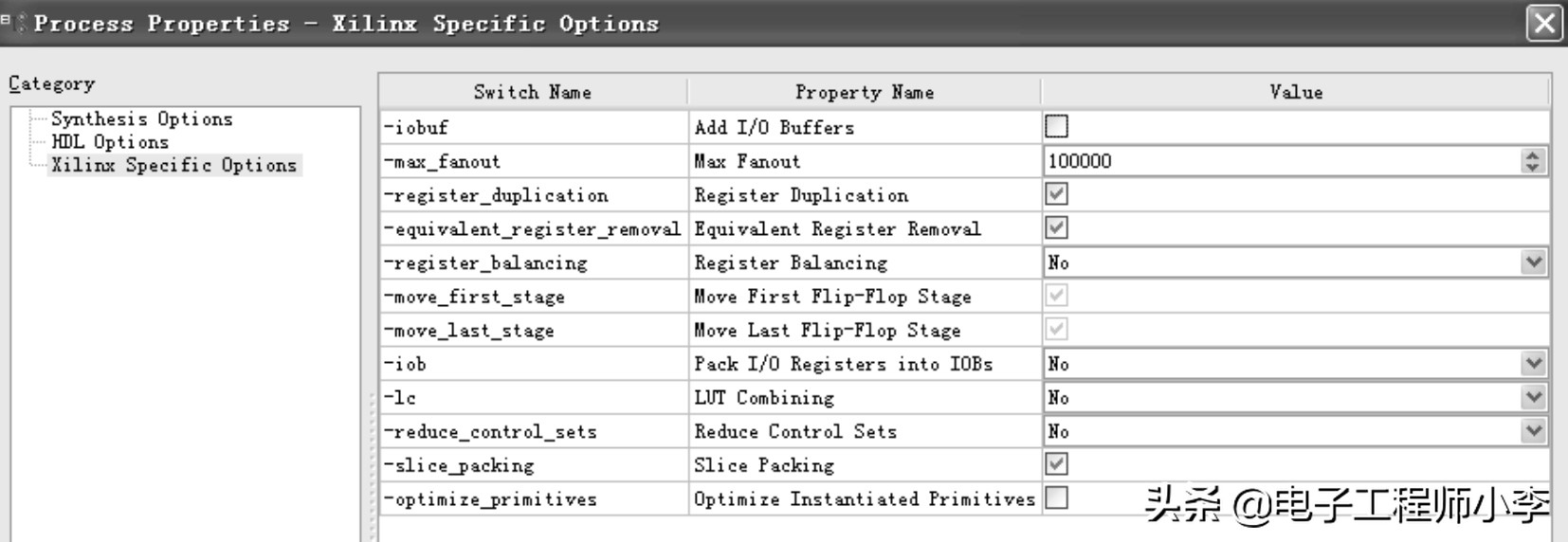

设置综合选项,综合过程中不能加入IO buf和iob(考虑到跟外部模块接口问题)。在综合设置中,-iobuf不要勾选,-iob选NO,如图3-39所示,综合生成网表led.ngc。

图3-39 综合设计选项

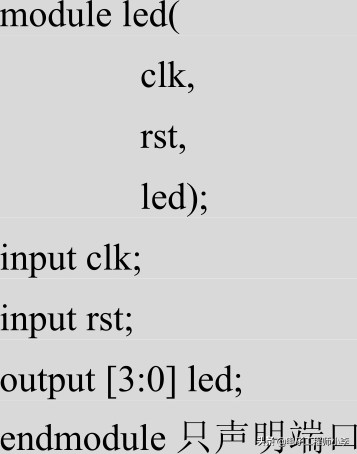

第2步:制作一个blackbox模块(就是一个IP的wrapper封装设计),Wrapper程序如下:

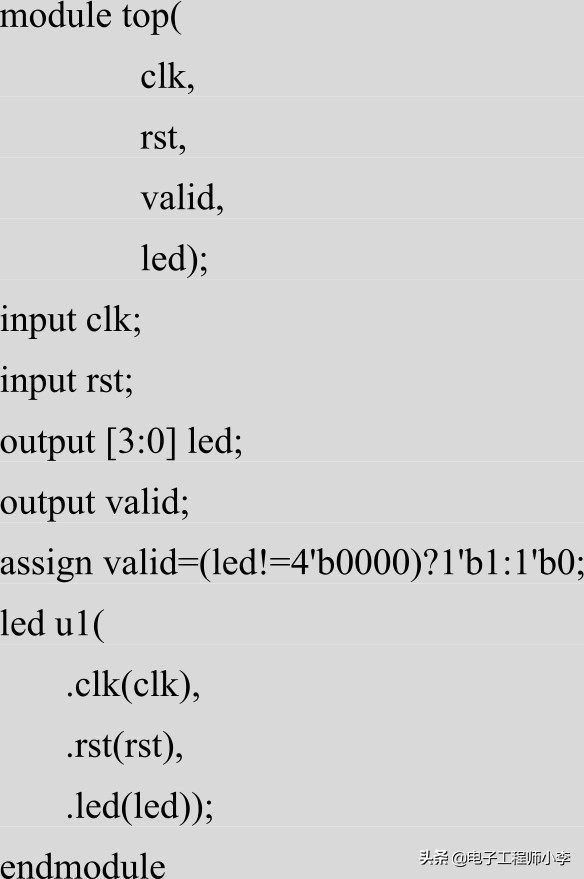

第3步:使用此IP,需要先把第二步的blackbox以v文件形式加入工程,调用这个模块,再把led.ngc文件加入工程文件夹下即可。

仿真波形如图3-40所示。

图3-40 仿真波形

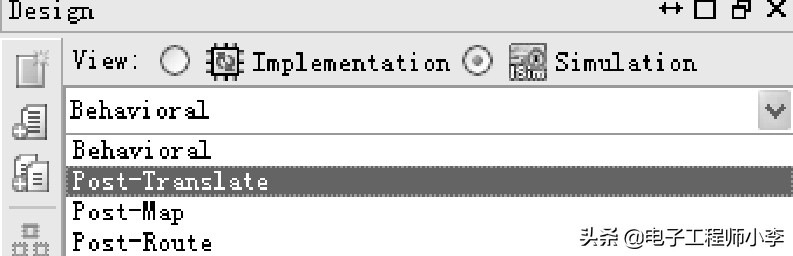

仿真的时候不能选择行为模式,只能选择后面三种,详见图3-41。

图3-41 选择仿真选项

另外,子模块和top不是同一款FPGA,只要顶层模块使用的器件包含子模块调用的逻辑资源就可以。