1. 像素结构(Pixel Architecture)

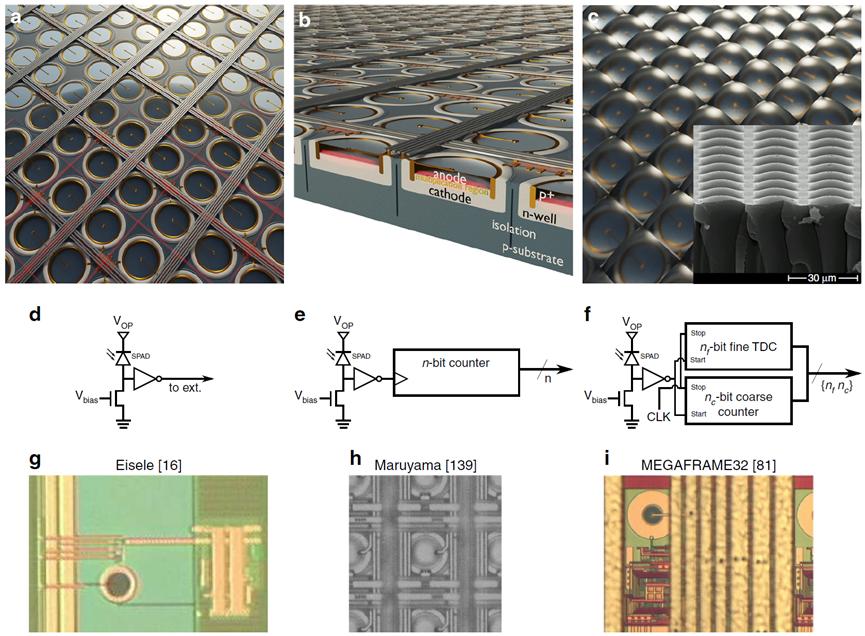

根据在光电转换基础上的功能不同,我们将SPAD像素电路分为三大类。第一种类型由基本结构表示,它只包括由雪崩的产生、猝灭和充电组成的完整检测周期所需的电路,这样一个像素的输出是一串对应于单个光子探测的电脉冲。第二种类型是带有内嵌计数器的SPAD像素,它由计数电路和至少一位存储器组成,输出为所记录的光子数。第三种像素是时间相关的,包括分辨光子到达时间的电路;它的输出可以简单到在给定时间窗口内的检测标志,也可以复杂到报告不同光子到达时间的可变数量的时间戳。下图中的d-f显示不同像素SPAD结构的概念图,g-i是典型的应用案例。像素的填充因子是由在组装阵列时与SPAD周围的电子设备数量的反比关系得到的,这样也更有利于使用现代制造技术来实现个更小特征尺寸的设计。

SPAD成像仪实现结构

所有类型的像素设计*共中**有的元素包括主动猝灭和充电、屏蔽和门控策略。有源猝灭和充电可以被用来优化一个SPAD的检测周期,主要是通过一种良好的控制方法来减少死区时间,从而可以提高检测周期的最大计数率。在这种情况下,有源电路可以用来阻止雪崩的发生,并且可以比被动电阻方法下更早地给SPAD充电。这不仅限制了流经二极管的电荷量,从而提高二极管的使用寿命,而且这种方法还可以减少寄生脉冲的发生。这种针对猝灭和充电的有源电路技术已经用于大量的设计方案中。

值得注意的是,探测到的SPAD光计数值,实际上对应于同时检测到的一个或者多个光子事件的发生,这种事件发生的确切数目是无法被分辨出来的(SPAD事实上也被称为点击事件探测器)。尽管如此,人们仍然可以在时间的尺度上利用对SPAD的猝灭和充电机制的预测,来估计所探测到的光子的数量。例如,在时间尺度上,撞击的光子数是呈指数型增加变化的。

有意思的是,掩膜可以被用来实现选择性的禁用或者导通阵列中的特定像素探测单元,该方案通常用于具有多个像素共享电路的设计中,以避免因特殊噪声像素的过载而导致的整体性能降低的问题。当然,这也可以备用实现对SPAD进行开关控制,从而可以防止不必要的雪崩的发生,或者可以将像素单元与读出电路断开,消除潜在的串扰。

门控技术又是像素体系结构中一个独立的设计元素,它指的是在有限的时间内控制SPAD的开关,这个时间窗口可达到皮秒量级。门控技术可直接应用于SPAD或者在其前端电子设备中,前者为器件控制门控,后者则为电子信号控制门控。在SPAD门控技术中,要么将阴极偏置降低到击穿电压以下,要么将阳极偏置增加到超出偏置电压以上,当SPAD在门控选中开启后,观测窗口随之打开。如果所需要的偏置高于CMOS电路的应用标准时,则需要额外的控制电路调节。然而,在这种情况下,由于外部门控线的电容的充放电作用,门的上升和下降时间增加了;相比之下,门控前端电子元件可以直接集成到CMOS电路中,从而实现更清晰的门控效果,但缺点是SPAD仍然在门控之外运作。因此,在这种情况下,必须在打开门之前对SPAD先进行充电。

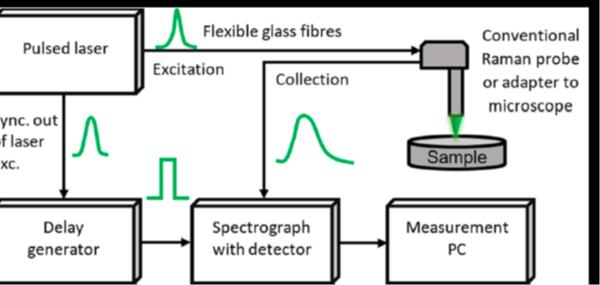

门控检测技术尽管整体检测效率降低了,但是其最大意义在于可以实现时间分辨探测。例如在具有重复(脉冲)照明的装置中,门控允许在重复周期的某个特定周期内选择性地捕获光子,从而实现了在皮秒级移动门控窗口来精准控制检测时序的功能。当然,这也可以实现滤除不感兴趣的那部分光子响应。典型的门控应用包括FLIM中的快速寿命测定,时域*特中**定光学响应的精确重建,早期/背景相关检测的消除,或拉曼光谱中样品固有荧光的减少。门控还可以通过消除发生在感兴趣的时区之外的暗计数来降低DCR。

荧光寿命成像技术

时间门控拉曼光谱技术

除了基本结构之外,像素还被设计为包含用于多种目的的内存元素。单位存储器可用于在给定的时间间隔(即帧时间)内捕获纯二值图像,例如在重要的是要避免全局快门工件时;这种架构只需要几个晶体管就可以实现,因此仍然允许可接受的填充因子(5-10%),而快速读取(10-100 kpfs)数据,这通常被用于增加动态范围和积累多位芯片外图像的需求中。

具有集成的到达时间测量的像素,通常可以实现时间到数字转换器(TDCs)或其模拟对象物(时间到模拟转换器或TACs),代表了最强大,但也是最复杂的像素架构。一般来说,定时电路需要尽可能地紧凑和低功耗,以便集成到成像器的每个像素中,同时要仍然能够提供所需的定时分辨率。

2. 阵列结构(Array Architecture)

最简单的SPAD阵列结构就是将SPAD像素单元排列成一行。在一维阵列中,所有的像素电子被放置在传感器区域之外,并且这个区域只有二极管监管分离不同像素的活动区域。尽管在原则上资源共享可以像二维阵列一样实现,不过大多数的线性SPAD阵列还是允许真正意义的并行像素操作。一维阵列结构的优点是可以实现最大的像素填充率,这是以牺牲二维图像所需的光学和机械扫描方案为代价的。

二维的SPAD像素阵列能够直接探测到被测物的二维图像信息,前提是需要实现像素单元和读出电子设备之间的相互关联,这往往需要更加复杂的传感器结构设计。一般来说,为了将填充率最大化,二维SPAD阵列中所有的供应、控制和数据信号都可以在阵列中的行和列共享像素单元。像素单元上所需的最小电路是线性读出电路,但通常也会添加更多复杂的电路,例如实现门控和带有内嵌计数器的电路。更为复杂的像素设计包括时间戳电子器件和像素内的光子信息计数或者时间预处理的功能。根据应用需求,一些电路元件,如复杂的时间-数字转换器,可以在多个像素单元之间共享,当然也可以在多行多列或者更大的像素块*共中**享。

尽管设计者尽力在二维SPAD阵列中想要最大化填充因子,但是依旧低于同尺寸的sCMOS相机,尤其是对于如含有晶体管计数更大的像素内TDCs这样的复杂像素架构。因此,微透镜代表了一种可行的选择,可以弥补由于电子器件而丢失的部分填充因子。这些微型光学器件被放置在敏感区域的前面,通常是在探测器的表面,并将光子集中到活跃的(即光敏的)像素区域,如第一张图中的C图所示。

在二维SPAD成像仪中,像素可能不再严格地并行工作,例如,当它们包含内存元素时,这些内存元素被寻址,然后由读取器逐行重置以收集新光子(称为卷帘采集操作)。当用非常快的动态记录现象时,这可能会导致众所周知的人的行为特征,例如反应时间导致的延迟。因此,一些成像器实现了一个真正的全局快门操作,它在给定的时刻提供了一个图像快照。这可以通过在帧开始时一起激活所有像素,然后在帧结束时“冻结”数据采集并开始读出操作来实现。一种不需要许多昂贵的全局信号的替代方案是由事件驱动的操作模式表示的,它允许在事件发生时连续动态地记录事件;实现这种操作模式的一种方法是使用由所有像素共享的公共总线(例如在一列中),使用单独的地址行来标识已经触发了的SPAD。

SPAD像素阵列有着较高的灵活度,可以针对不同的应用场景需求做出相应的调整和预处理。例如,对于飞行时间正电子发射断层扫描造影术(ToF-PET),目标对象是伽马射线的能量、到达时间和相互作用信息。伽马射线通过闪烁晶体转化为可见光光子,由SPAD阵列或者SiPMs探测。在这种情况下,通过将多个SPAD阵列分组在一起并使用掩膜来补偿检测器噪声,降低记录数据的有效粒度是有意义的。在这种数字方法中,伽马射线能量由在几百纳秒的时间窗口内发射的SPAD器件的总数给出,而到达时间可以在芯片上估计,并通过本地控制和通信FPGA进行细化。

3. 读出结构(Read-out Architecture)

当与单光子相机接口时,特别是在记录单个光子的时间戳或在非常高的帧率下工作时,一个主要的问题是将会产生高数据速率。最终,数据速率需要降低到可以传输到计算机或存储介质的水平。这是可以实现的,例如,使用与条纹相机相同的方法,即在非常短的时间内将捕获的信息以高速率存储在本地(像素中),然后以低速读出以用于处理和存储。

另一种可能是对更高层次信息实行就地提取。相应的算法,如直方图累积或多位计数积分,可以通过控制FPGA结构实现,甚至也可以在传感器本身上实现。例如,在荧光寿命成像的情况下,已经设计出了实时呈现系统,可以以视频速率计算分子的寿命,而不需要记录完整的单光子数据流。FPGA系统确实在可能的数据处理和高计算带宽方面提供了一些灵活性,例如,可用于实现基于固件的32×32个自相关器数组(以FCS作为目标)。也有文献中提出“可重构像素”概念,通过移动整个电路,最大限度地提高灵活性,通常放置在FPGA内部的基本SPAD像素结构中;这使得实现不同的TDC或计数器体系结构成为可能,目标是根据目标应用场景的需求以最佳方式定制系统(包括传感器和固件)。