【 硬件的单元测试_1】电源与时钟的测试概述

【硬件的单元测试_2】信号完整性测试概述

【硬件的单元测试_3】PCIe 3.0及信号完整性测试方法

【硬件的单元测试_4】USB3.0测试

【硬件的单元测试_5】电源纹波测试

注意示波器的探头和示波器本身的带宽能够满足测试要求。

测试点的选择要注意选到尽量靠近信号的接受端。由于 DDR 信令比较复杂,因此为了能快速测试、调试和解决信号上的问题,我们希望能简单地分离 读/写比特。

此时,最常用的是通过眼图分析来帮助检查 DDR 信号是否满足电压、定时和抖动方面的要求。触发模式的设置有几种,首先可以利用前导宽度触发器分离读/写信号。

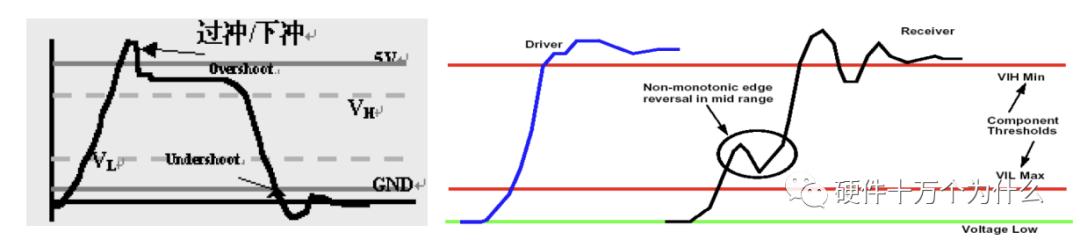

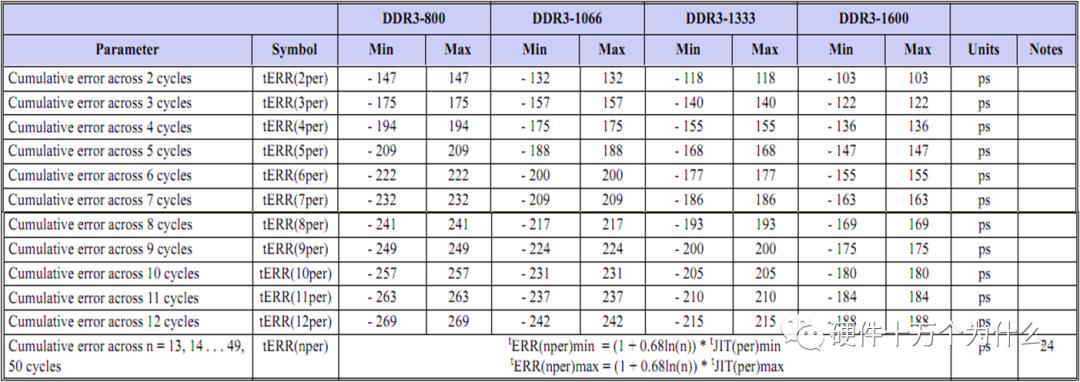

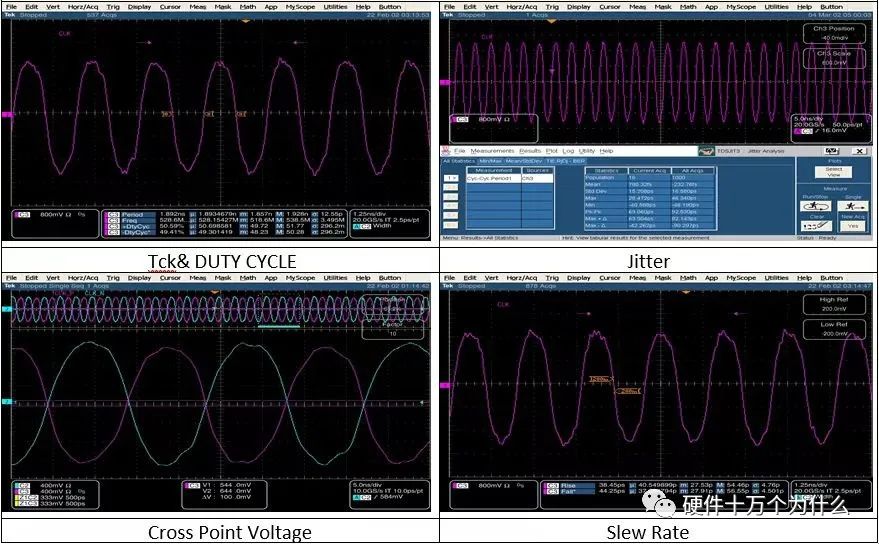

根据 JEDEC 规范,读前导的 宽度为 0.9 到 1.1 个时钟周期,而写前导的宽度规定为大于 0.35 个时钟周期,没有上限。第二种触发方 式是利用更大的信号幅度触发方法分离读/写信号。通常,读/写信号的信号幅度是不同的,因此我们可以 通过在更大的信号幅度上触发示波器来实现两者的分离。测试中要注意信号的幅度,时钟的频率,差分时钟的交叉点,上升沿是否单调,过冲等。

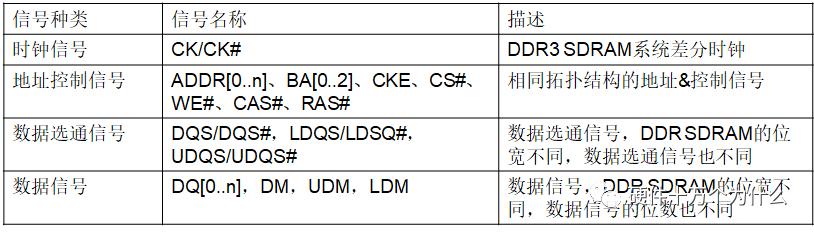

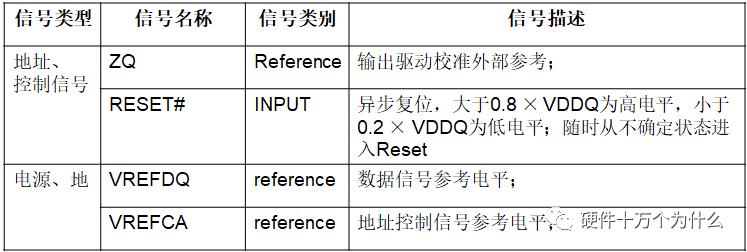

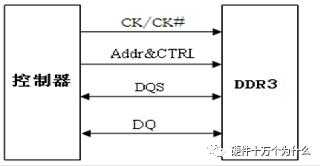

1、DDR3 SDRAM信号按功能分类

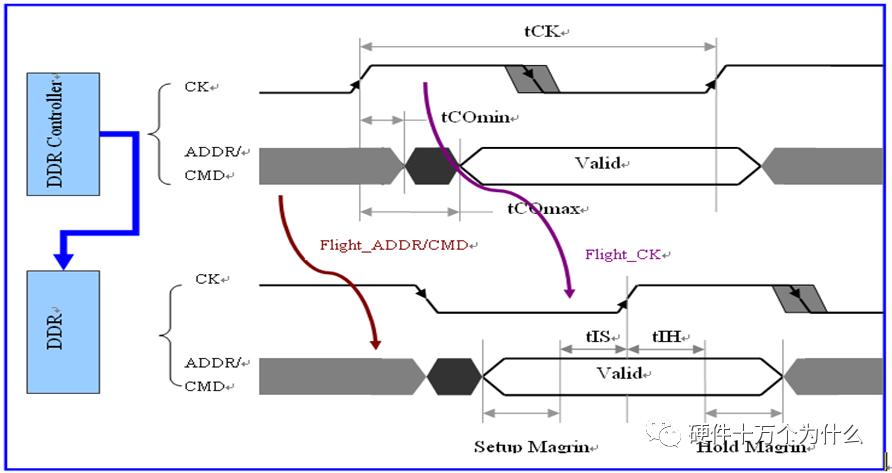

2、DDR3中的几种采样关系

地址控制信号ADDR/CMD与系统时钟CK的时序关系

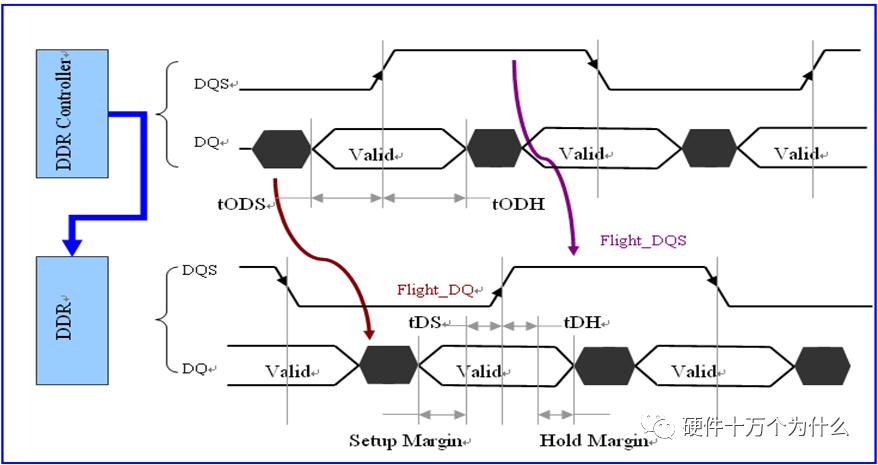

数据信号DQ/DM与数据选通信号DQS的时序关系

写周期

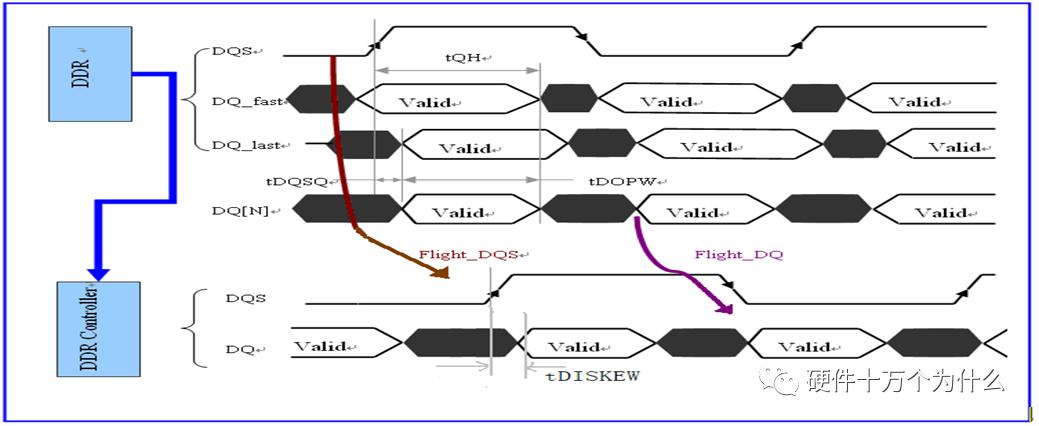

读周期

几种时序关系,后续会做详解

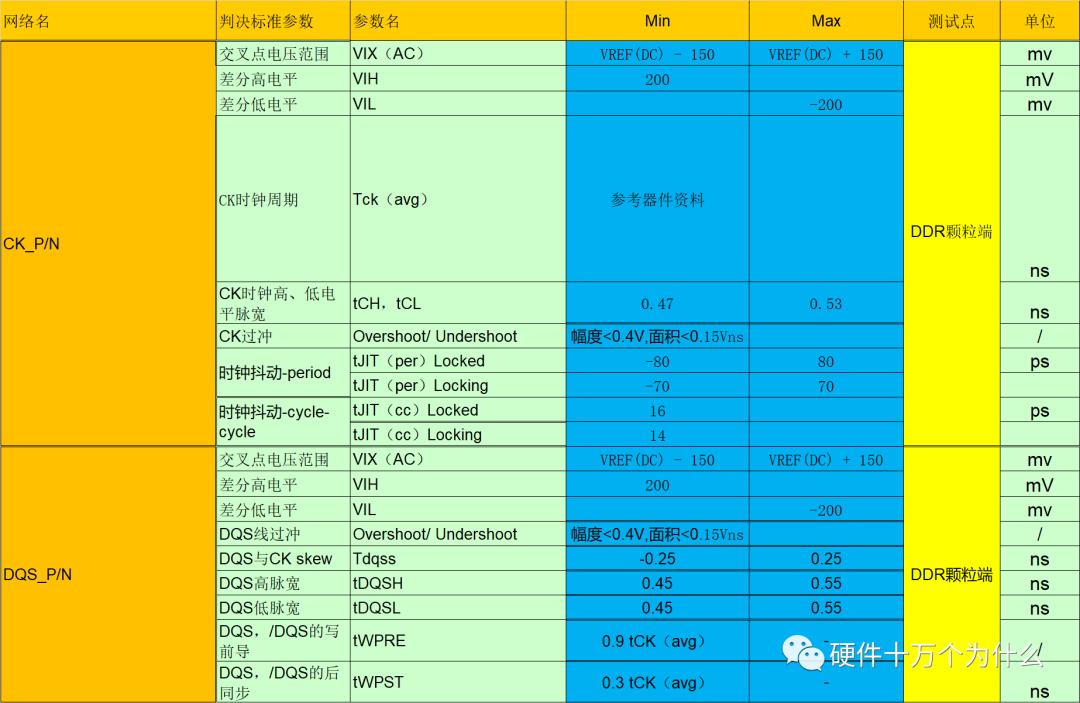

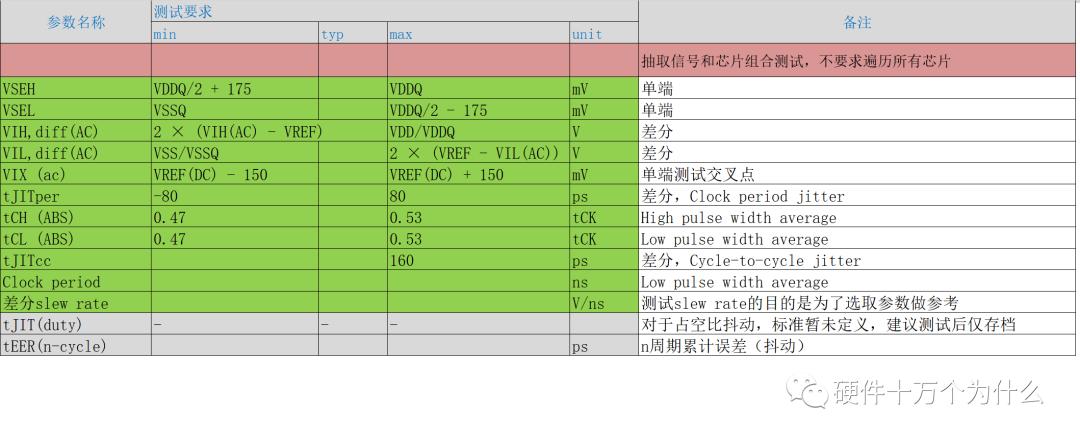

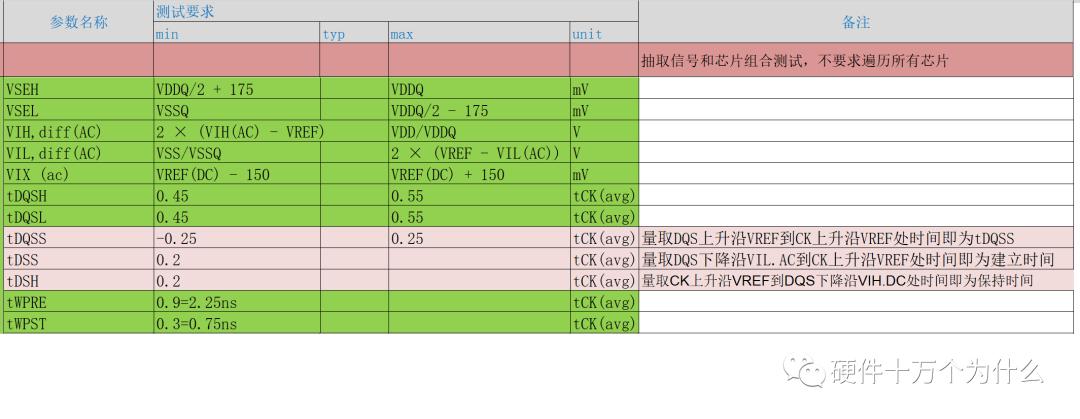

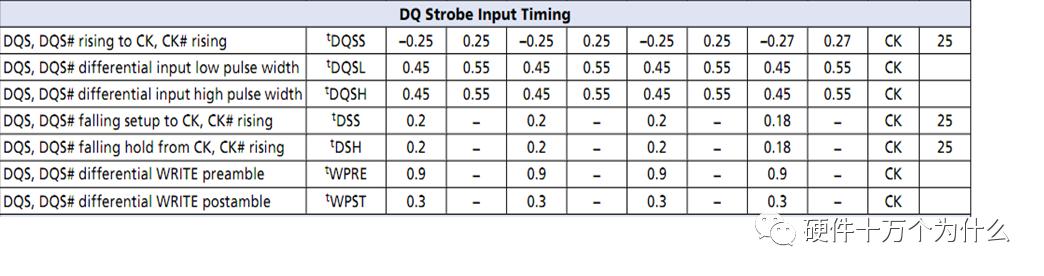

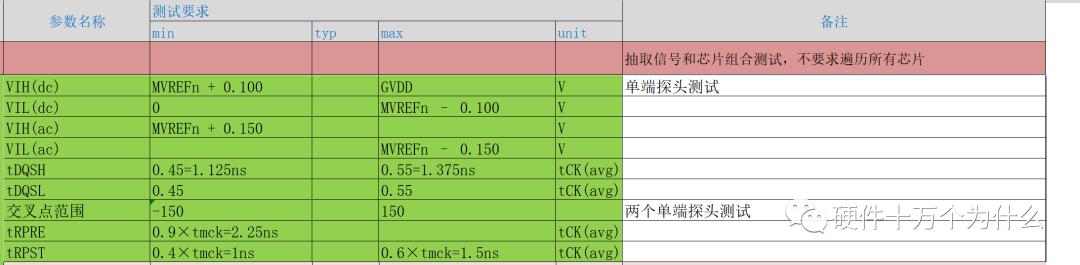

3、DDR时钟信号(CK、DQS)测试:

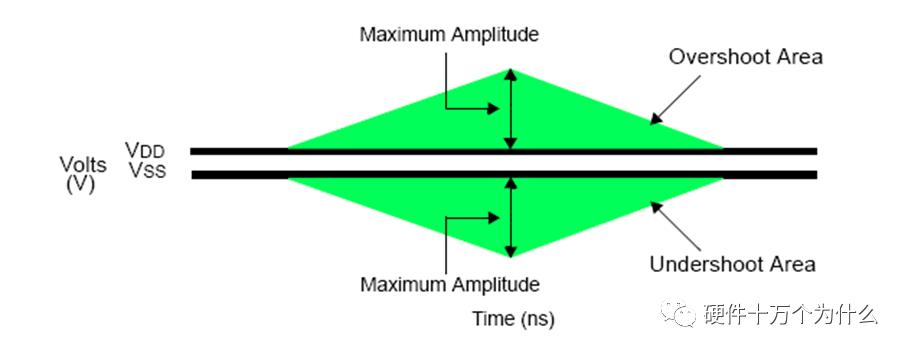

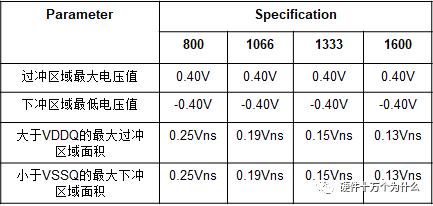

时钟信号过冲要求

写方向

CK

DQS

读方向

【 硬件的单元测试_1】电源与时钟的测试概述

【硬件的单元测试_2】信号完整性测试概述

【硬件的单元测试_3】PCIe 3.0及信号完整性测试方法

【硬件的单元测试_4】USB3.0测试

【硬件的单元测试_5】电源纹波测试

——书籍推荐——