尊敬的模拟IC工程师们:

作为欧洲模拟 IC 最有名的大牛之一,Sansen对基本电路的论述既细致全面、又深入浅出。从一个电路的低频到高频的小信号输入阻抗,输出阻抗,增益开始到各类运放、及其构成的反馈系统,无所不精。

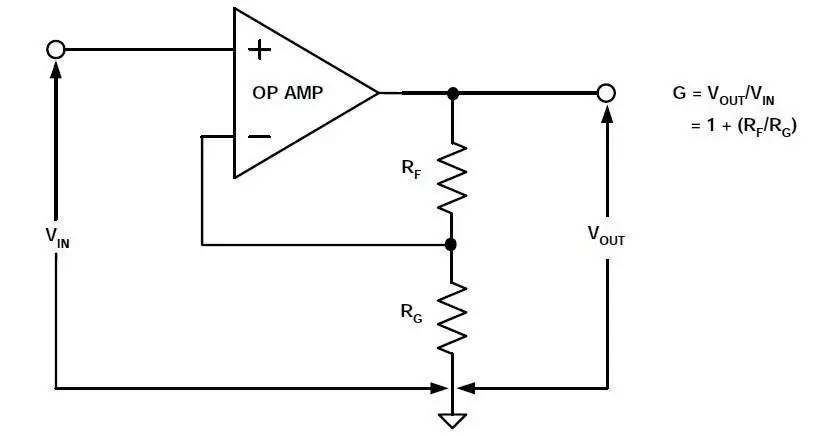

其中,运放是各类模拟电路的基础,运放的环路增益、反馈系数、频响特性,决定了整体电路的性能参数。

运放的框图看上去如此简单,可是每个设计过运放的宝宝,都知道实际的工作可不是这么简单

因为每一个电路设计的开始,都是从公式计算开始的。

铺开一张白纸,提起一支笔,那感觉和铺开一张画图,进行构图设计的感觉,是一样一样的。用基本的公式算出主要输入管、输出管的参数、补偿电阻的参数,整个电路框架初定,就像一张画图上大面积的色块开始上了色。

然而,不管是调电路的工程师,还是画画的画家都明白,这样就算是一个好的电路完成了么?显然不是,从基本参数、到完美电路,这中间的距离才是设计师的心血所在,也是设计师专业功底的体现

接下来,如同细细的描摹一幅山水画、笔墨深浅为画注入灵魂;抑或是一幅工整的油画,每一笔描绘、每一笔着色,深浅浓淡之间,就让一幅简单的底色逐渐生动起来。模拟IC设计艺术家们,开始调整运放的密勒补偿、cascade、gain-boosting,每个管子的尺寸,电容、电阻的大小,加dummy, 在那种精细的调整中,犹如猛虎嗅蔷薇。同时还要考虑到layout的工整、面积大小,以及后仿真对电路参数的影响。

这个时候,如果可以去观察一个模拟IC工程师的工作,他的每一个工作都蕴含着深意,他的每一次调整都是方寸之间令人惊叹的闪挪腾移,就会发现工作中的工程师如此魅力迷人,和忧郁不羁的艺术家魅力不相上下。

这就是模拟电路的魅力,一个人眼中有一千个哈姆雷特,一千个模拟IC设计师手下也要一千个不同的电路,即使设计的是同一结构的电路。

如此充满生机与个性的的模拟电路,在测试的时候,自然也会碰到那些微妙的千变万化的差异。今天我们就来分享几类典型的模拟及混合信号IC及其测试方法,让大家充充电,找回当年“沉溺学习,无法自拔”的自己,更好的领略在工程技术中的艺术气质,以及像艺术一样的灵感对工程技术的启迪与创新。

1、运放环路增益测量

2、高速 ADC 技术的发展趋势及测试方法

3、是德科技模拟 IC 测试方案

1

运放环路增益测量

作为模拟电路中的基础单元,运放的特性直接决定了上层电路的关键性能,尤其是PMU类的电路,整个儿环路增益的测试,一度成为很多电源芯片管理设计师的难点。

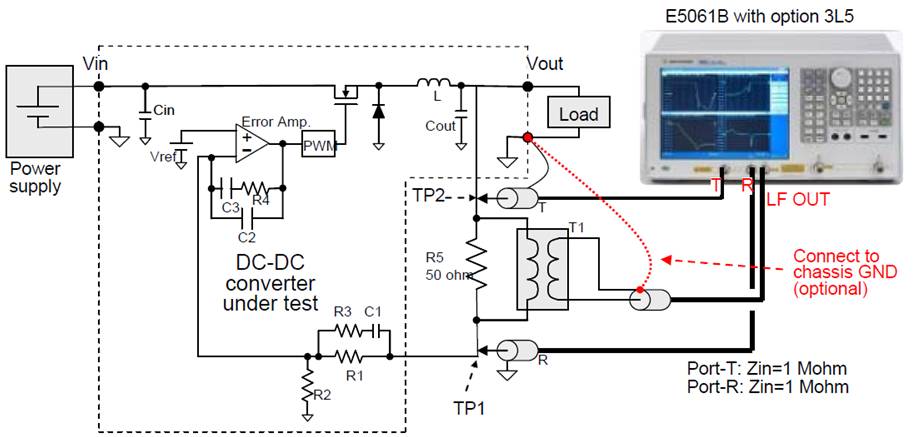

工欲善其事,必先利其器,使用 Keysight E5061B-3L5就可以测试环路增益、相位裕量、增益裕量等反馈环路特性。比如环路增益测试测试配置如下图:在E5061B-3L5的高输入阻抗测量接收机的R和T端口上测量激励施加电路两侧的交流电压,随后把这两个测量结果进行比值计算得到环路增益最终的测量结果。

-

把激励信号加在满足Zin >> Zout 的点上,并让电阻R满足Zin >> R >> Zout的条件,可以通过T/R 比值的测量结果得到循环传递函数-GH 的特性,这里选择R=R5=50欧姆;

-

注入激励信号的电平不能太高,以避免反馈环路进入非线性区域。应使用高输入阻抗的探头来完成探测,这样不会影响反馈环路的工作;

-

由于E5061B半浮置的接地结构,仪表的激励源与接收机端口相对被测器件的接地也是浮置的。在使用10:1无源探头测量时,为了避免更多的耦合杂散,需要将LF OUT屏蔽层与被测DC-DC电源的地连接。

-

在测量中使用直流电子负载或大功率电阻作为DC-DC电源的负载;

-

即使反馈环路测量最关心的是交叉频率附近(通常在10KHz-100KHz之间),当激励源的功率为固定值时,为了改善在低频测量范围内环路增益测试的信噪比,需要使用在低频范围频率响应平坦的变压器。推荐使用是德科技5188-4425变压器,或者North Hills公司的0017CC变压器。

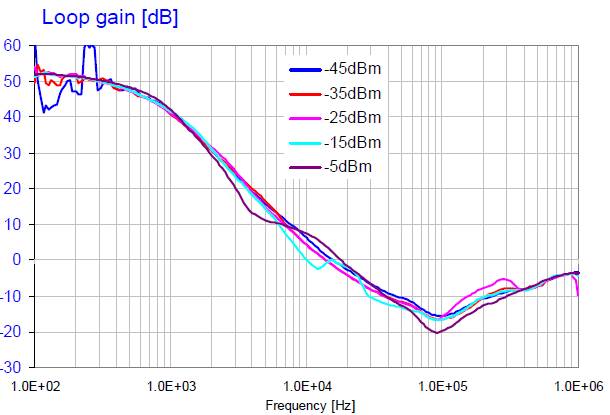

如下图所示,当测试得到环路增益|GH|后,通过游标找到|GH|=1的交叉频率。同样的,在相位测量曲线即可得到相位裕量,进而可以测量增益裕量。

使用E5061B-3L5测试DC-DC环路增益、相位裕量、增益裕量以及电源系统PDN阻抗的系统配置如下:

-

E5061B(Opt: 005,3L5) 网络分析仪

-

1250-1250(x2),15442A

-

85033E

-

11667L

-

8120-1840(x4)

-

16201A(Opt:001),16195B

-

16092A,16192A(16192A/B/C/D,16197A根据需要选择),16047E

2

高速 ADC 技术的发展趋势及测试方法

随着数字信号处理技术和数字电路工作速度的提高,以及对于系统灵敏度等要求的不断提高,对于高速、高精度的ADC(Analog to Digital Converter)、DAC(Digital to Analog Converter)的指标都提出了很高的要求。比如在雷达和卫星通信中,所需要的信号带宽已经达到了2GHz以上,而下一代的5G移动通信技术在使用毫米波频段时也可能会用到2GHz以上的信号带宽。虽然有些场合(比如线性调频雷达)可能采用频段拼接的方式去实现高的带宽,但是毕竟拼接的方式比较复杂,而且对于通信或其它复杂调制信号的传输也有很多限制。

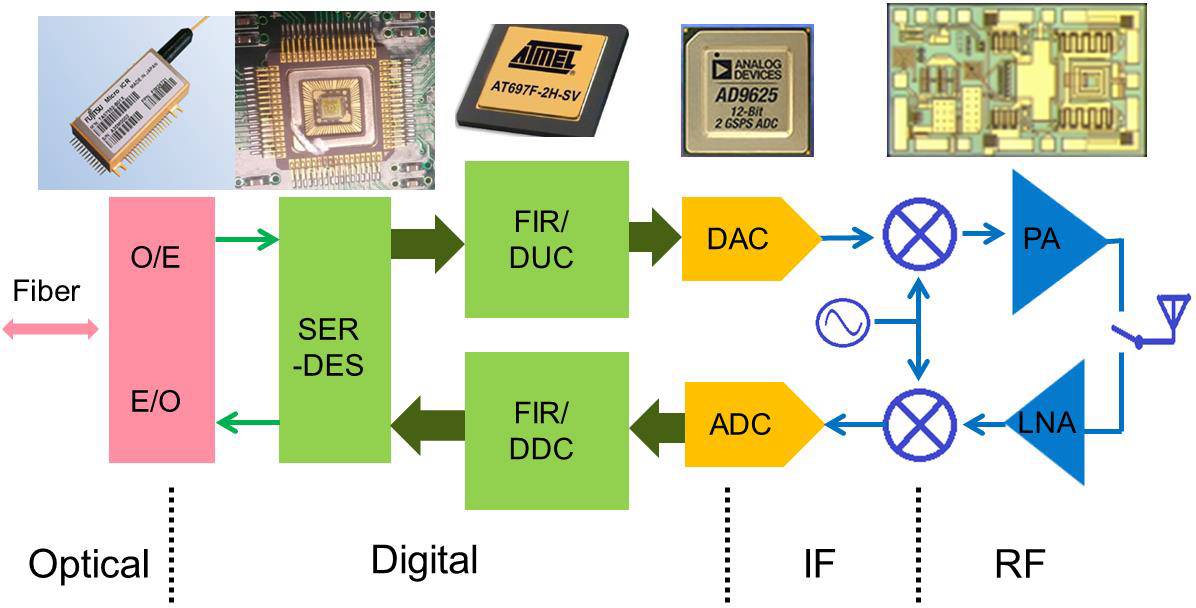

根据Nyquist采样定律,采样率至少要是信号带宽的2倍以上。同时为了支持灵活的制式、相控阵或大规模MIMO的波束赋形,现代的收发机模块越来越普遍采用数字中频直接采样,这其实进一步提高了对于高速ADC/DAC芯片的性能要求。下图是一个典型的全数字雷达收发信机模块的结构。

高速ADC/DAC在现代全数字雷达中的应用

可以看到,ADC/DAC芯片是模拟域和数字域的边界。一旦信号转换到数字域,所有的信号都可以通过软件算法进行处理和补偿,而且这个处理过程通常不会引起额外的噪声和信号失真,因此把ADC/DAC芯片前移、实现全数字化处理是现代通信、雷达技术的发展趋势。

在全数字化的发展过程中,ADC/DAC芯片需要采样或者输出越来越高的频率、越来越高带宽的信号。而在模拟到数字或者数字到模拟的转换过程中造成的噪声和信号失真通常是很难补偿的,并且会对系统性能造成重大影响。所以,高速ADC/DAC芯片在采样或者产生高频信号时的性能对于系统指标至关重要。

目前在很多专用领域,使用的ADC/DAC的采样率可以达到非常高的程度。比如Fujitsu公司可以提供110G~130GHz的IP核,Keysight公司在高精度示波器里用到了单片40GHz采样率、10bit的ADC芯片,以及Keysight公司在高带宽任意波发生器里用到了92GHz采样率、8bit的DAC芯片等。这些专用的芯片通常用于特殊应用,比如光通信或者高端仪表等,比较难以单独获得。

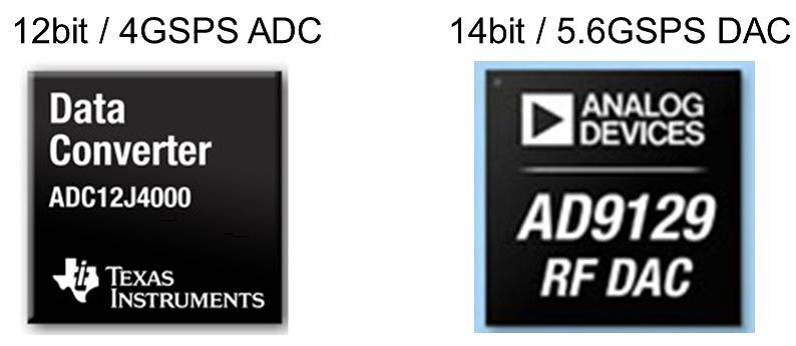

在商用领域,很多ADC/DAC芯片的采样率也都已经达到了GHz以上,比如TI公司的ADC12J4000是4GHz采样率、12bit分辨率的高速ADC芯片;而ADI公司的AD9129是5.6GHz采样率、14bit分辨率的高速DAC芯片。这一方面要求ADC有比较高的采样率以采集高带宽的输入信号,另一方面又要有比较高的位数以分辨细微的变化。

随着ADC/DAC的采样率的提高,高速ADC/DAC的数字侧的接*技口**术也在发生着比较大的变化。

-

低速串行接口:很多低速的ADC/DAC芯片采用I2C或SPI等低速串行总线把多路并行的数字信号复用到几根串行线上进行传输。由于I2C或SPI总线的传输速度大部分在10Mbps以下,所以这种接口主要适用于MHz以下采样率的ADC/DAC芯片。

-

并行LVCMOS或LVDS接口:对于几MHz甚至几百MHz采样率的芯片来说,由于信号复用后数据速率太高,所以基本上采用并行的数据传输方式,即每位分辨率对应1根数据线(比如14位的ADC芯片就采用14根数据线),然后这些数据线共用1根时钟线进行信号传输。这种方法的好处是接口时序比较简单,但是由于每1位分辨率就要占用1根数据线,所以占用芯片管脚较多。

-

JESD204B串行接口:对于更高速率的ADC/DAC芯片来说,由于采样时钟频率更高,时序裕量更小,采用并行LVCMOS或LVDS接口的布线难度很大,而且占用的布线空间较大。为了解决这个问题,目前更高速和小型化的ADC/DAC芯片都开始采用串行的JESD204B接口。JESD204B接口是把多位要传输的数据合并到一对或几对差分线上,同时采用现在成熟的Serdes(串行-解串行)技术用数据帧的方式进行信号传输,每对差分线都有独立的8b/10b编码和时钟恢复电路。采用这种方法有几个好处:首先数据传输速率更高,每对差分线按现在的标准最高可以实现12.5Gbps的信号传输,可以用更少的线对实现高速数据传输;其次各对线不再共用采样时钟,这样对于各对差分线间等长的要求大大放宽;借用现代Serdes芯片的预加重和均衡技术可以实现更远距离的信号传输,甚至可以直接把数据直接调制到光上进行远距离传输;可以灵活更换芯片,通过调整JESD204B接口里的帧格式,同一组数字接口可以支持不同采样率或分辨率的ADC芯片,方便了系统更新升级。

ADC的主要性能指标分为静态和动态两部分:

-

主要静态指标:

Differential Non-Linearity (DNL)

Integral Non-Linearity (INL)

Offset Error

-

主要动态指标:

Total harmonic distortion (THD)

Signal-to-noise plus distortion (SINAD)

Effective Number of Bits (ENOB)

Signal-to-noise ratio (SNR)

Spurious free dynamic range (SFDR)

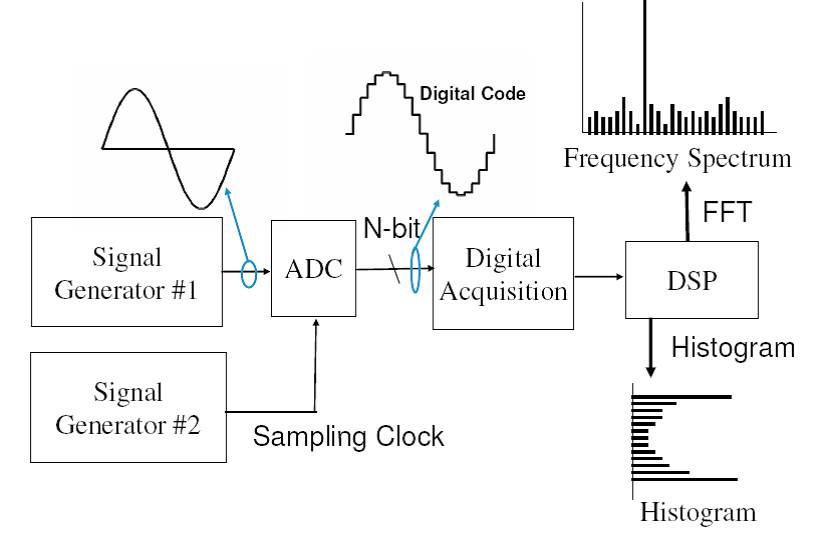

要进行ADC这些众多指标的验证,可用的方法很多。最常用的方法是给ADC的输入端提供一个理想的正弦波信号,然后对ADC对这个信号采样后的数据进行采集和分析。因此,ADC的性能测试需要多台仪器的配合并用软件对测试结果进行分析。下图是最常用的进行ADC性能测试的方法。

在测试过程中,第1个信号发生器用于产生正弦波被测信号,第2个信号发生器用于产生采样时钟,采样后的数字信号经FFT处理进行频谱分析和计算得到动态指标,经过直方图统计得到静态指标。

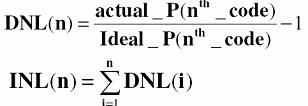

静态指标是对正弦波的采样数据进行幅度分布的直方图统计,然后间接计算得到。如下图所示,理想正想波的幅度分布应该是左面的形状,由于非线性等的影响,分布可能会变成右边的形状,通过对实际直方图和理想直方图的对比计,可以得出静态参数的指标。

以下是DNL和INL的计算公式:

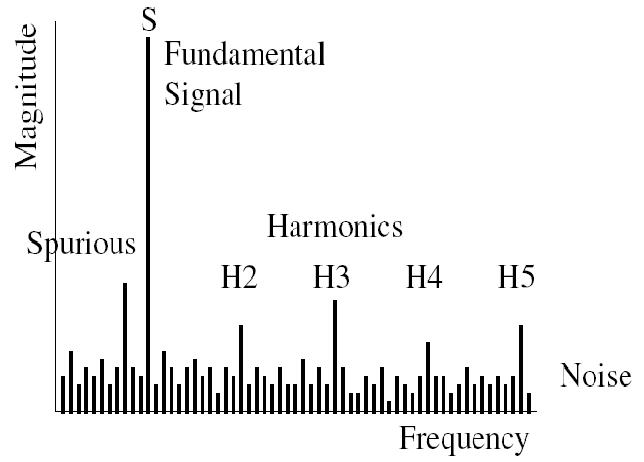

动态指标是对正弦波的采样数据进行FFT频谱分析,然后计算频域的失真间接得到。一个理想的正弦波经A/D采样,再做后频谱分析可能会变成如下图的形状。除了主信号以外,由于ADC芯片的噪声和失真,在频谱上还额外产生了很多噪声、谐波和杂散,通过对这些分量的运算,可以得到ADC的动态参数。

通过FFT频谱分析测试动态参数

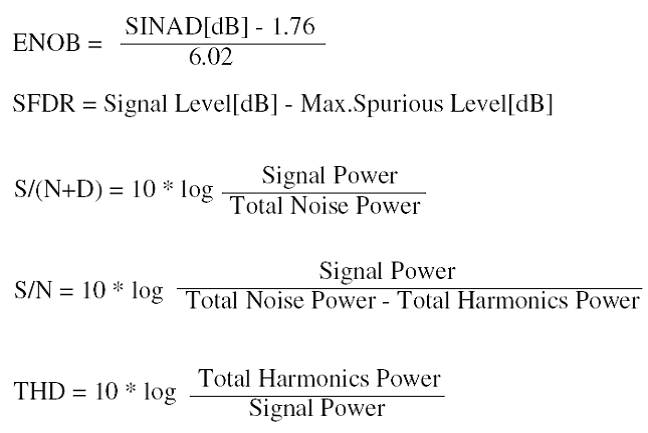

下面是动态参数的计算公式:

对于产生被测信号和采样时钟的信号发生器来说,为了得到比较理想的测试效果,要求其时间抖动(或者相位噪声)性能要足够小,因为采样时钟的抖动会造成采样位置的偏差,而采样位置的偏差会带来采样幅度的偏差,从而带来额外的噪声,从而制约信噪比的测量结果。下图是时钟或者信号抖动引起信噪比恶化的示意图,以及根据信噪比要求及输入信号频率计算信号抖动要求的公式。

3

是德科技模拟 IC 测试方案

随着数字信号处理技术数字电路工作速度以及系统灵敏度的不断提高 高速、高精度的 ADC、DAC 指标也面临着越来越严苛的挑战。

比如在雷达、卫星通信、图像采集等应用领域中,很多 ADC/DAC 芯片的采样率都已经达到了 GHz 以上。这一方面要求 ADC 有比较高的采样率以采集高带宽的输入信号,另一方面又要有比较高的位数以分辨细微的变化。因此,保证 ADC/DAC 在高速采样情况下的精度是一个很关键的问题。

一个典型的 ADC 测试方案

ADC/DAC 芯片的性能测试是由芯片生产厂家完成的,需要借助昂贵的半导体测试仪器,但是对于板级和系统级的设计人员来说,更重要的是如何验证芯片在板级或系统级应用上的真正性能指标。

而在验证各个指标的时候,测试设备和测试方案的选择从一开始就需要我们慎之又慎。下面就给大家安利一篇技术长文《Analog IC 模拟芯片测试》,高速 ADC 的测试方案、DAC 测试的配置方案、PLL/VCO 的测试方案……应有尽有,助您全方位把控模拟 IC 测试方案,保证 ADC/DAC 在高速采样情况下的精度。

请长按,识别下方二维码

或点击“阅读原文”*载下**相关文档

👇

长按,识别图中二维码,*载下**PDF文档

希望各位模拟工程师在是德科技的帮助下,能够做出传世的“艺术品”

是德科技 2017.6.9

关于是德科技

是德科技是一家领先的技术公司,致力于帮助工程、企业和服务提供商客户优化网络,进而将其电子产品以更低的成本、更快地推向市场。从设计仿真到原型验证、再到生产测试以及网络和云环境的优化,是德科技提供了全方位电子信号测试与分析解决方案。我们的客户遍及全球通信、航空航天与国防、汽车、能源、半导体和通用电子终端市场。2017 年 4 月,是德科技完成对 Ixia 的收购。Ixia 公司在网络测试、可见性和安全解决方案领域具有十分雄厚的实力。更多信息,请访问 www.keysight.com

长按,识别上方二维码

关注 是德科技官方服务号

点击“阅读原文”*载下**模拟 IC 测试方案