想在次贴讨论阻性/感性/容性/电流型负载对驱动的要求。

大家指正一下;看看有啥不足,谢谢!

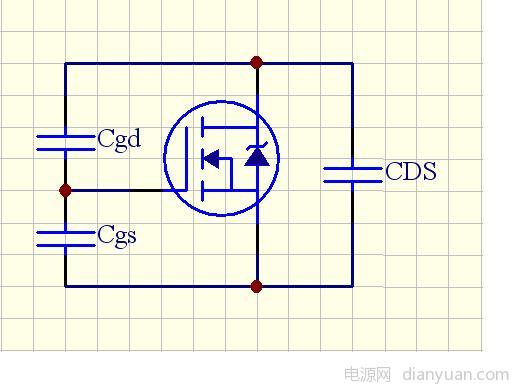

在之前的文章中(手把手教你读懂FET),大家讨论过,FET的等效模型是:

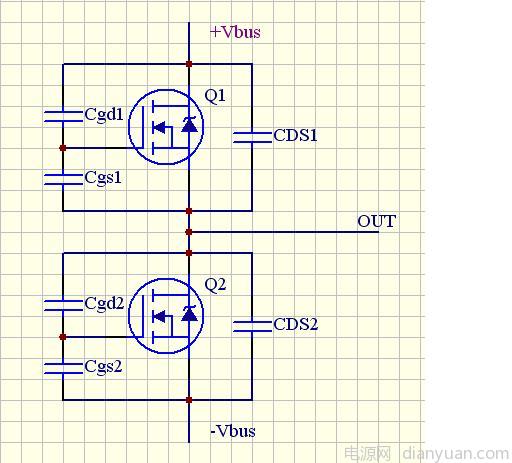

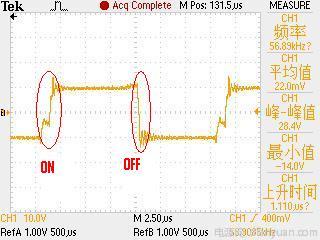

用它做成的半桥;就成了这样的一个电路:

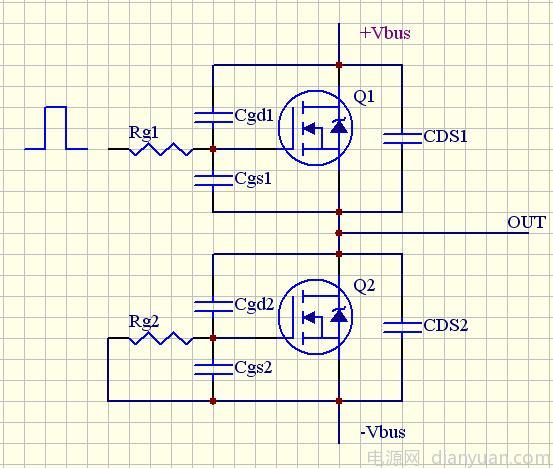

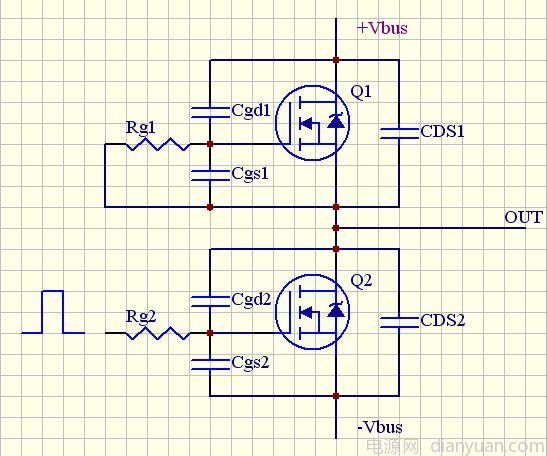

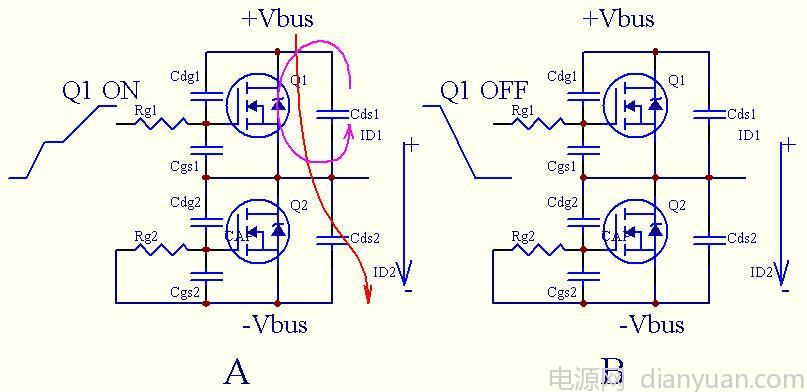

空载开关时;电路变成这两个工作模式:

上图是高边开关;低扁关断状态。下图是低边开关;高边关断状态。两个状态组成一完整开关周期。

这个现象会导致半、全桥空载时发热。它不仅发生在开路状态;而且还会发生在容性负载和硬开关电路里。

适当的控制“开”的速度;防止上下之通是必要的。

高端FET开关状态下;导通再关闭后,由于CDS1、CDS2的电容储能,Q1关断;输出仍为+Vbus。此时;Q1栅电压为0V,但是;Q1并没因此而承受电压。

即Q1是零电压关断;关断过程;栅电压没有平台!没有弥勒效应区!

试着画个关断过程中;Q1的栅电压波型。

经过一段死区时间后;低端FET导通,此时此刻;高端早已关断的FET的D-S终于承受了电压!虽然是空载;但在这过程中发生了一系列的电压电流变化,看图解!~

高边FET导通后;向Cds2充电/Cds1放电,输出达到正电源电压。FET关断时;由于电容无放电回路(Q2断),电容电压保持不变,Q1零压管断(无弥勒效应)。Q1关后;仍由于电容作用而不承受电压。

Cdg1/Cds1没有电;Cdg2/Cds2电被充到满电源电压。

用正驱动脉冲开启Q2,当栅电压达到门坎时;Q2开始通。Cds2短路放电;Cds1充电。显然;Q2是硬开通。Q1此时开始实质性承受电压。

由于Cdg1的充电;导致在Q1驱动栅电阻上产生电压。当感应电压达到门坎时;Q1/Q2瞬间发生上下直通。

半个周期描述结束,思考一下;下半周期的工作过程。

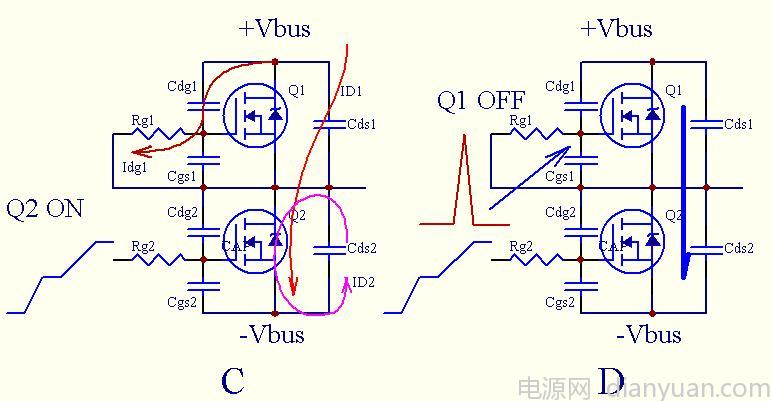

低端的管子是硬开通软关断;高端皆然。这里引用网友helen闸的实测波形,供大家讨论。注意:“ON”是;有明显的弥勒效应平台,“OFF”时;没有。

这个现象会导致半、全桥空载时发热。它不仅发生在开路状态;而且还会发生在容性负载和硬开关电路里。

适当的控制“开”的速度;防止上下之通是必要的。

因此;如果将线路理想化,只从器件本身而言。FET需要在开和关时;不同的驱动速度。两者之间的比值设为

λ=Ion/Ioff

极限值为λo

当驱动比小于λo,桥不会直通;反之就有这情况发生。

感性负载刚好和容性相反,FET一关;电压将急剧变化;以至对侧FET在负压下;寄生二极管通。在电感续流作用下,电流不断;二极管就无法恢复到阻断状态——无论经过多长死区时间!

在下半周期;FET开通时;就会和这个二极管发生直通。直通电流大小和栅电阻有直接相关的关系。

想想这是啥过程?为什么?

FET开的越快;栅电压升的越陡,FET的饱和电流越大。短路电流就越大。

注:短路时;FET完全工作在线性区。

所以;在感性负载里,栅电阻的最小值受FET寄生二极管反向恢复特性的限制。最小弥勒效应区基本时间基本和实际反向恢复时间相当。

FET的反向恢复时间和电流/结温和FET规格都有关系。一般建议用寄生二极管在典型满载下的实际反向恢复时间为准;选取FET开通回路的驱动栅电阻。

阻性负载:

大体和容性相当,只是半桥输出在死区时间里;电压是电源电压的一般(如果同同样的FET做的半、全桥的话)。

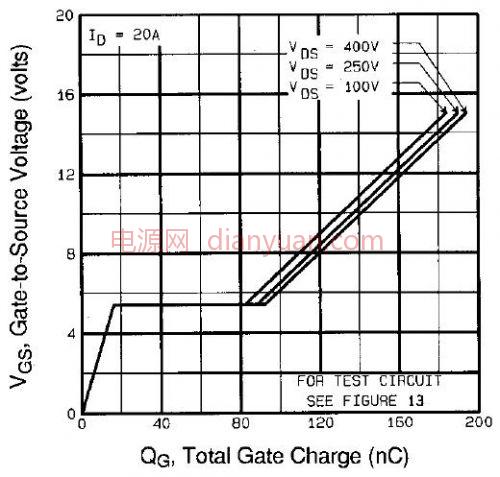

由于FET在关断后;没有承受所有电压,FET实际的弥勒效应略微减小。看这图:

Vd的减小;使弥勒效应提前结束,真是这样吗?为什么?

对于实际器件;由于有杂散电容影响,只有足够大电流在能有这个现象。否则就会呈现软开关或容性负载了。

弥勒效应是弥勒电容在电路里;物理作用的体现。

因此;可以用软开关来抑制弥勒效应。典型的做法就是让电路工作在ZVS状态。

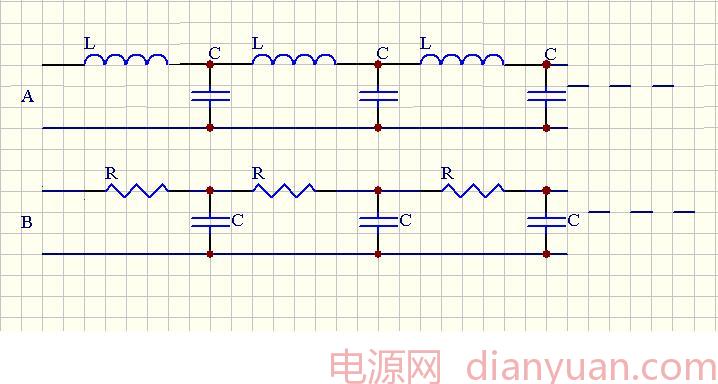

现实负载中;除了电容/电感/电阻性负载外。还有一类负载;叫高分布参数负载。如大功率PFC/电机/PDP驱动等等。它们大体可以等效成这样两种拓朴(单级或多级链接)

当你用方波驱动这样的负载时;电压或电流高/射频分量会发生反射。地线上充满梳装噪音,在方波沿上;同时跳动着电流尖刺。驱动速度越高;间刺越大。

(这和我们用不同阻抗同轴电缆连接电视;而产生重影是一个道理)

如果拉开波型;可以发现,第一个电流尖峰是最高且貌似正弦。这个现实的脉冲电流就是这个网络产生的。

这时候;大体有三种选择:

1)串低分布参数的电感,使分布电容的作用减到最小。

它对负载端的分布参数抑制有效;对FET自身寄生电容没作用。

2)用低分布参数的元件做开关,开的足够快。快速开关后;连联线都可以被等效成电感了。

效率提高了,元件要求高了,需要增加EMI/C网络了

3)开慢些;再慢些,所有寄生参数变的越来越无足轻重了。

牺牲了效率,提高了EMI/C品质

4)用软开关拓朴

元件增加了;效率提高了;噪音下来了;成本提高了

你喜欢哪种?平时常用哪种?

可能每个人都有这样经历;在人/车多的地方说话;周围总有或大或小的响动掺在你要听的声音里。这些响动就是噪音,它总是在干扰你听到有用的声音。

同样;电路里也有这样的情况。总有些或高或低;起伏变化的信号叠加在器件信号输入口上(如逻辑IC的输入端口;IGBT/FET的栅等)。这些能够干扰用信号;甚至淹没的电信号就是电磁噪音。

大多数的器件是接在地线上的;信号发出和接受;都是以地线为参考。地线上是否有噪音;决定了系统是否可用和如何抑制的方法。因此;大多数情况下;都是以地线为研究对象。

电源;是电与场的统一体。电磁噪音;是磁和电联合起来做恶的负面效果。消其一;就没了协作能力,噪音就能降一个量级。

所谓磁电分离;及控制噪音源的电场或磁场辐射。在两者同时抑制有困难时;只要消掉一个;EMI/C噪音就会降低。

典型磁噪音源:变压器 PCB线 元件引线等

典型场噪音源:FET 散热器 变压器 功率PCB线

在所有负载中;最奇怪的要数电机负载。做过的工程师可能都有这样的体会;驱动板到电机连线的长度;会对电磁噪音的大小和频谱有明显的影响。

这事同样会发生在大功率电源中。

大分布电容;导致驱动速度被限制,除非在输出线上串低分布电容的电感。

驱动与散热器接地。

功率稍大些;功率器件就需要安装在散热器上。一般;散热器有三种处理方式:

1)悬空

2)经过安规电容接地

3)直接接热地

在开关电路里;有两个器件的dV/dt最高:功率开关和变压器或电感。

功率管的散热背板刚好和散热器完美耦合!

为了散热;绝缘垫薄了又薄,导致耦合电容大了又大(绝缘封装也是一样的,它只是提前穿了件绝缘马夹),电磁噪音被散热器很好耦合。而散热器的功用;导致它的体积不小。它就成了开放式天线,向空间辐射着耦合来的电磁噪音。

如果有兴趣;打开电源可以拿台收音机,离上数米的距离收听电源那吵杂流水的噪音。

那时;你会发现散热器越大;噪音越厉害。

散热器悬空或通过电容接地时;就是一对地的开放或连接的电容。这个电容有辐射(开路时)和电荷积累两重功效。

辐射自不必说;看看收音机里的可调电容就能明白。

关于电荷积累,发生在管子和散热器间有绝缘垫的场合。由于散热器到地和元件到散热器间有电容,这两个电容实质是串联关系。这样的每个实物电容是理想电容和泄漏电阻的并联。由于大小不等,在高频交流的作用下,散热器将会带上寄生电荷,到一定程度后;就会打火花。

驱动越快;电容耦合越好;打火现象越厉害。在不增加器件的条件下;适当控制开关速度才能有效减少问题。

延伸讨论:

- 何为噪声呀?他的波形是?为什么在地线上测试呀?

可能每个人都有这样经历;在人/车多的地方说话;周围总有或大或小的响动掺在你要听的声音里。这些响动就是噪音,它总是在干扰你听到有用的声音。

同样;电路里也有这样的情况。总有些或高或低;起伏变化的信号叠加在器件信号输入口上(如逻辑IC的输入端口;IGBT/FET的栅等)。这些能够干扰用信号;甚至淹没的电信号就是电磁噪音。

大多数的器件是接在地线上的;信号发出和接受;都是以地线为参考。地线上是否有噪音;决定了系统是否可用和如何抑制的方法。因此;大多数情况下;都是以地线为研究对象。

- 测试了一下是这种现象.我从光耦的地到高压电容的地这间测试有1000MV左右的是不是噪音呀?我的示波器是100M的.测试方法跟测试纹波差不多.探头上没有加任何东西.请问有什么不对吗?

所有测试都不能啥都不接(悬空)啊!那是空间噪音;和板子上的不一样。

测共模噪音时;地线夹的连线要缠在探头上;探头和地线夹要短接在一起。测哪;就将探头搭到哪就可以了。差模噪音的频率一般比较低;直接用探头和地线夹去测就可以了。

PCB在高频时;呈现的是类似电感特性,高频电流会在上面产生电压降。

几乎所有的噪音都来自电磁分布参数。

- 关于噪音方面的控制方法吗?比如跟那些有直接关系呢?

控制策略很简单;无非就是减源增效。

减:就是减少噪音源。

增:就是抑制电/磁场辐射。

在开关电源里;噪音源主要有三个:

1)FET:开关产生高速升降的方波沿。沿越陡;射频分量越多。减缓开关沿就可以减弱噪音量。

减缓沿有两个方法:

①加大栅电阻。原理见【手把手 教你读懂FET】这篇文章

②选用软开关拓朴。受到参数限制;这个方法对高频段噪音抑制有效,对低频段效果可能不十分理想。优点是效率高。

2)二次整流管。主要由恢复特性和变压器漏感的组合造成EMI噪音。选用软恢复管可以减弱噪音。

3)高压整流桥。由于整流;电源电流不在零电压下过零,使分步LC在非零状态下产生二介过度过程,引起电磁噪音。通过在二极管上并电容;使之满足过阻逆状态,达到消噪目的。

通过控制这三个源;就能有效减弱电磁噪音。

这只是主原则。先看变压器分布电感的影响和对策。

变压器分布电容有两个组成:

1)一/二次间绕组的分布电容。在开关过程里;这个电容和冷热地间的Y电容构成回路,在每个沿都被充放电。沿越陡;充放电流越大,噪音也越大。电容越大;要求的Y电容也越大(两个电容是串联关系,Y电容越大,二次开关噪音越低),开关噪音能量越大,频谱越低。

2)匝间分布电容,这个联斗引起的是近似方波的电流噪音,主要集中在12M左右频带。变压器越大;频率中心区越低。

显然;许多优化方向是相互矛盾的。对于硬开关变压器;希望有比较小的漏感,那么;需要用一/二次绕组交换叠绕(千层饼法)。可这显然加大了一/二次间耦合电容。

一/二次欧合回路里;包括这两个电容外;还有引线电感。它们构成了LC噪音倍增网络(电磁场互相叠加了)。

从梯型波的富利叶展开可以看到,当沿的时间慢于周期一半时;该次以上谐波量会迅速衰减。

从这个理论;我们可以找到一个方向;控制沿的斜率来抑制噪音。因此;Y电容的位置和变压器的绕法和大小及PCB布线都将影响我们能用的最高开关沿的速度。

合理的PCB设计允许有高的开关速度。

因此;通常设计的电源里,我们把开关沿控制在50~150nS水平。大功率电源的变压器分布电容大,为了实现高效;只能降低点频率了。

这也是现在广泛关注软开关拓朴的原因。在软开关电路里;尽可能的将最快沿控制在150~250nS范围。

在硬开关电路里,可以用弥勒效应控制开关速度。

在软开关电路里;可以用分布电容了感性无功环流来控制沿的时间范围。一般;FET在软开关拓扑里的驱动弥勒时间要短于沿时间的1/2。但;要长于FET寄生二极管的反向恢复时间。