最近UCIe横空出世,为了方便大家更好地了解UCIe,本文根据UCIe的白皮书总结而成。

UCIe是什么的缩写?

UCIe是Universal Chiplet Interconnect Express

UCIe的愿景是什么?

创造一个开放的片间互联生态

UCIe和PCIe有什么区别?

PCIe主要提供了处理器和外设之间的连接标准,并没有考虑如果处理器芯片和外设芯片同在一个封装内部情况。通常做法保留PCIe上层协议,裁剪物理层以适应片上连接需求。UCIe将能够弥补这部分的空白。

UCIe的性能目标是什么?

高带宽,低延时,高能效,高性价比

UCIe能帮助到哪些应用?

计算,存储,云,边缘计算,企业,5G,自动驾驶,高性能计算,手持设备等

UCIe可以怎么连?

没有UCIe之前,片上多die互联通常由同一家公司完成设计,同一家Fab用一种芯片制程进行制造并封装。UCIe希望未来能够提供对不同Fab生产的芯片,或是不同设计公司的芯片,甚至不同的制程的die进行互联。

为什么需要不同制程的die进行互联?

在芯片的众多功能模块中,只有部分功能模块需要更先进的制程用于提升其性能和降低功耗,例如计算核,协处理核,缓存等,对于其他模块,可以采用n-1或者n-2制程,这样一来,既可以降低更换制程的设计费用,也可以继续使用现有工艺提供更好的产能,加速整体产品推向市场。

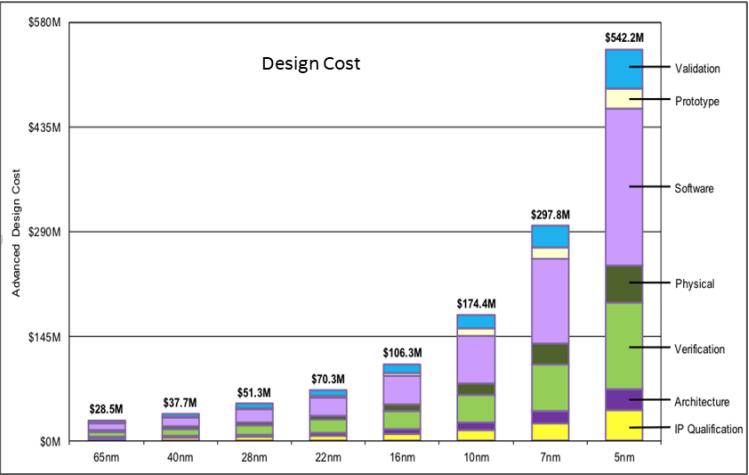

下面可以看看不同制程下的设计费用:

UCIe协议的层次结构是怎样的?

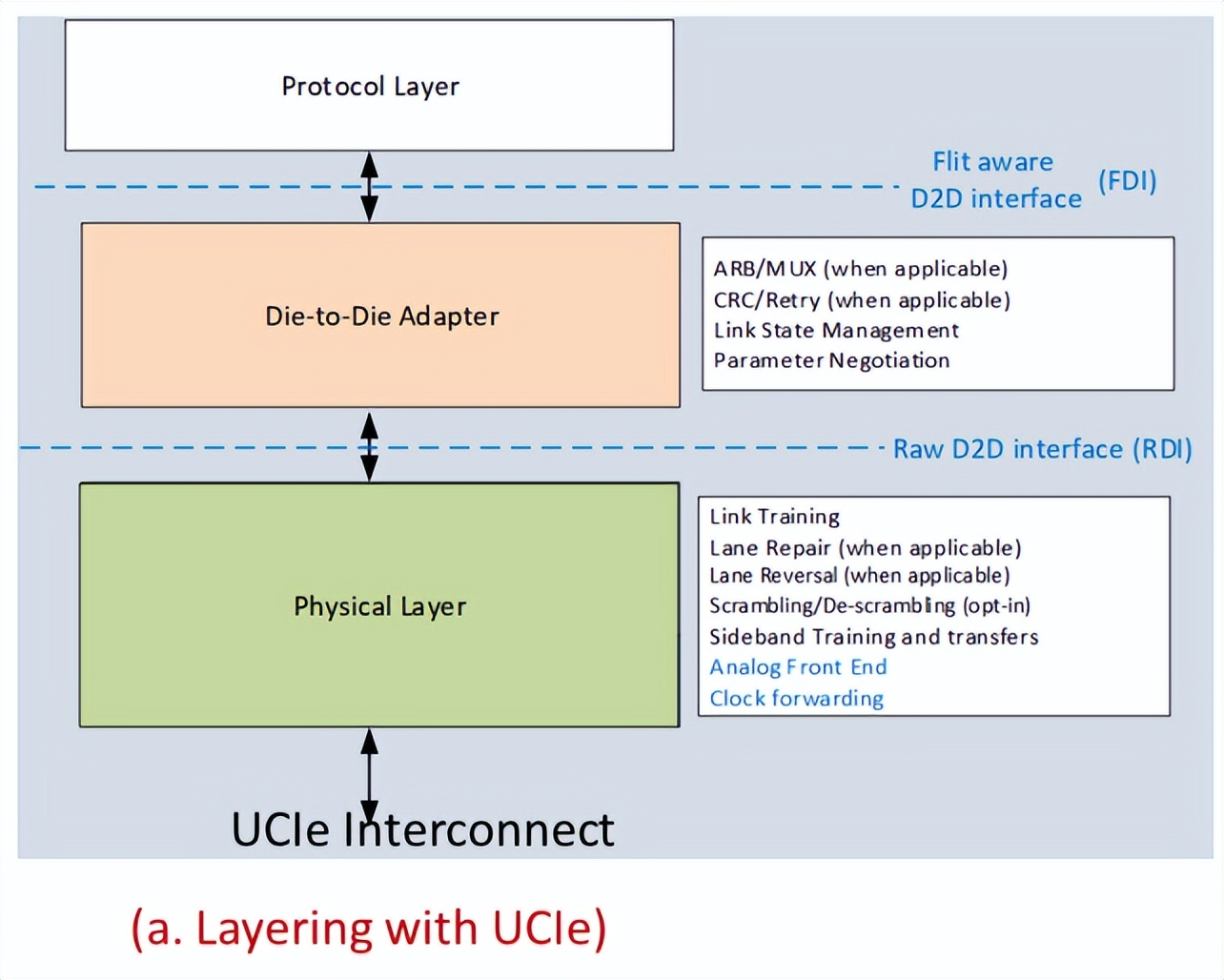

UCIe分成三层:(如下图所示)

物理层主要提供电气信号,时钟,链路训练和带外信号等。

Die-2-Die Adapter主要提供链路状态管理,信用管理,chiplet间参数交换等。虽然die-2-die的距离不算远,但仍然提供保障数据完整性的方案,例如CRC校验和重传机制等。

对于上层协议,UCIe只提供了Flit级别的接口(目前定义为256-byte),并支持多种不同的上层协议,例如PCIe,CXL等等。如有需要,在Die-2-Die层也会提供仲裁器协助不同协议间的切换。

目前看,PCIe和CXL协议是天然支持的,因为UCIe也是Intel主导的,但UCIe提供了streaming protocol可以映射到其他任何协议。当然,初期这种映射的性能可能堪忧,但UCIe承诺在未来会根据需要优化对其他协议的支持。

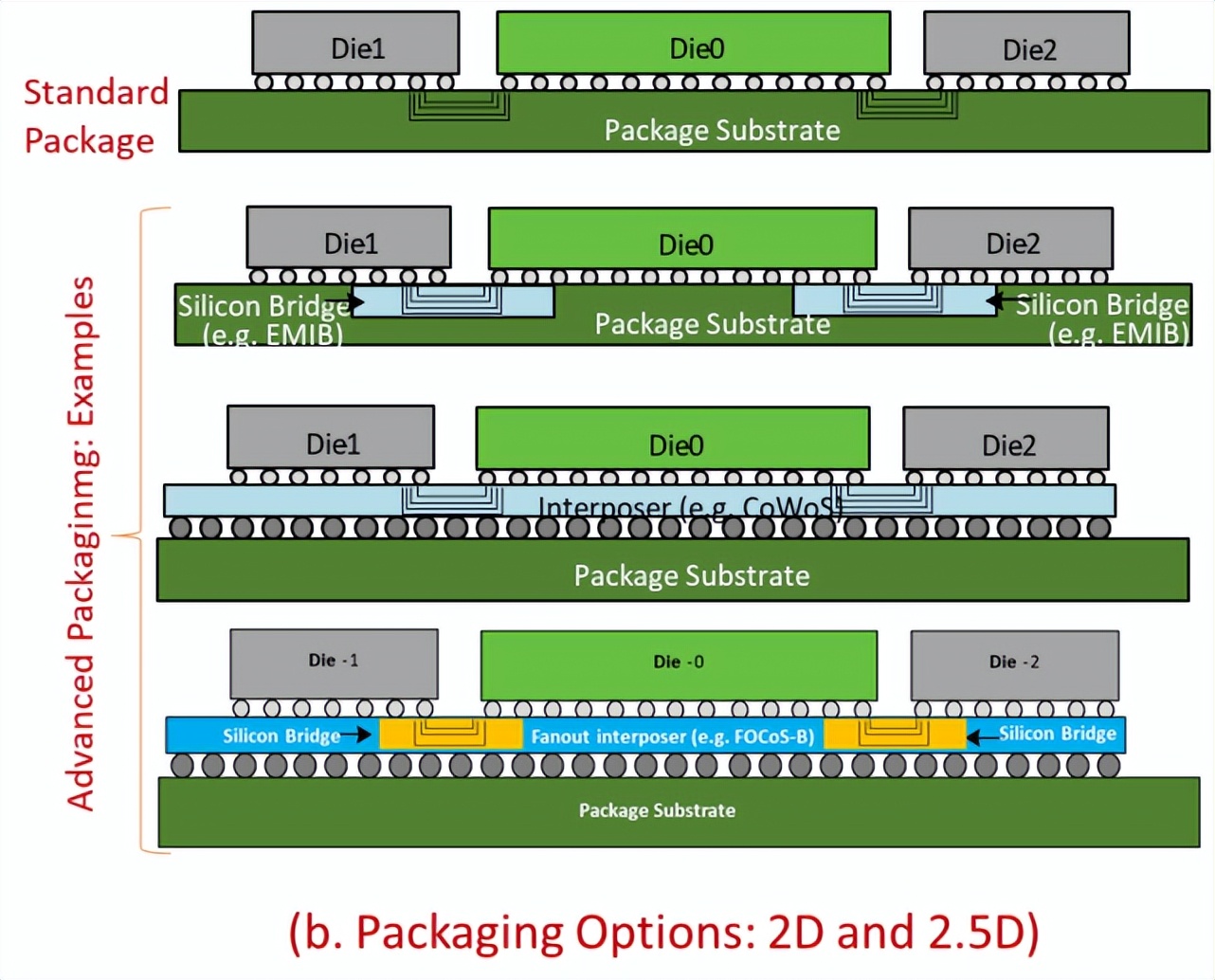

UCIe支持哪些封装(Package)?

如下图所示,UCIe支持传统2D封装,这种封装技术有较大的成本优势,但性能和功耗上可能需要有所取舍。

UCIe也支持更加先进的封装形式,例如Intel的EMIB (Embedded Multi-Die Interconnect Bridge),台积电的CoWoS (Chip-on-Wafer-on-Substrate),AES的FOCoS (Fan-out-Chip-on-Substrate)等,因为芯片驱动无需考虑传统Package Substrate的损耗,这些技术可以有效降低传输的功耗。

UCIe有哪些使用场景?

第一种使用场景是将原来板级系统的部件,集成到一个封装下面,例如内存,加速器,网卡设备等。

第二种使用场景是提供非封装类型的连接方式,例如通过光缆,铜缆,毫米波等,无需通过封装转换而直接采用UCIe的retimer就能将其承载的上层协议,例如PCIe或者CXL协议,在rack甚至pod level进行传输。不过目前没有看到具体的解决方案,具体细节可能要等到组织成立后继续讨论了。

UCIe目前的能力范围是怎样的?

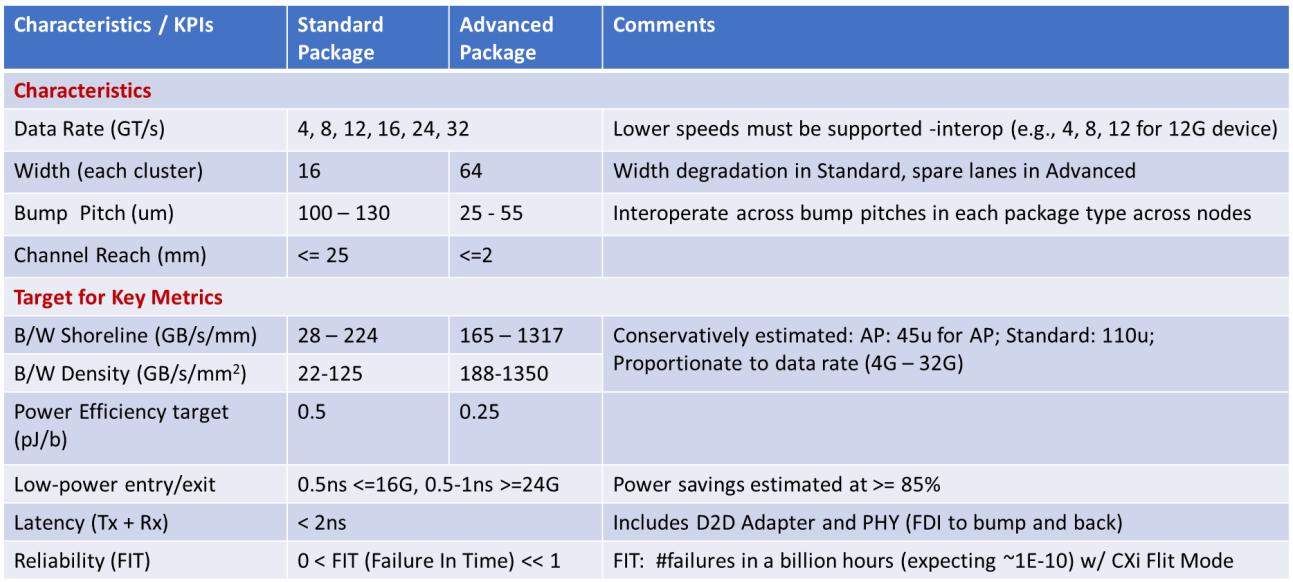

如下表所示:

UCIe从传输速率,Link宽度,Bump Pitch,通道物理长度等方面给出了具体的范围。其性能符合当前技术趋势。看来其主要的目的还是希望通过一套协议标准建立起互联生态,而技术创新本身可以作为未来追求的目标。

什么是Chip?

Chip就是集成电路芯片的意思。

什么是wafer?

又称为slice或者substrate,中文翻译为晶圆。Wafer其实是薄饼的意思,是不是用披萨更加形象?

什么是die?

通常IC制造是将一个芯片设计复制很多份到晶圆上,当晶圆完成了整个制造流程后,需要把晶圆切成一个个的小芯片,这个切成小方块的动作英文叫diced,中文叫切丁,这每个小方块就被称为了die,中文称为色子。

什么是SoC?

SoC是System-on-Chip的缩写,主要想表达的意思是一块芯片集成了全部或者大部分计算系统的组件,这些组件可能包括CPU,内存,I/O接口,显示模块,存储接口等等。

什么是Package?

因为芯片比较小,为了让芯片更好地和母版相连,以及提供必要的保护和散热支撑,芯片封装技术应运而生。

什么是multi-die design(多die设计)?

一个大型的芯片设计被切分成了多个小die设计,也被称为chiplets或者tiles,然后通过单一封装将这些小die组合起来,共同实现功耗和机构上的要求。封装形式上可以并列放置多个小die或者堆叠,例如目前流行的2.5D或者3D的封装技术。

什么是chiplets?

和传统单一芯片(例如SOC)不同,一个Chiplet只是一小块芯片用于完成单一芯片中的部分功能,多个相同或者不同功能的chiplet封装在一起共同提供与传统SOC芯片相同的完整功能。

Chiplets的优点是什么?

随着日益增长的性能需求,die的尺寸越来越大,例如多核的服务器处理器,GPU和Switch芯片等。与此同时,越来越先进的制程导致芯片单位面积的故障点增加等等。

对比传统单一芯片设计,chiplets设计能够在更小制程时提供:

- Die的尺寸越小,在同样故障点的情况下,能提供更好的良品率

- 同一个功能模块die可以复用到不同的产品中,为不同需求的客户快速提供整体解决方案。

- 不同的功能模块可能对制程要求不同,chiplets有机会提供不同制程的die间的互联(例如利用UCIe)

参考:

https://www.uciexpress.org/_files/ugd/0c1418_c5970a68ab214ffc97fab16d11581449.pdf

https://www.wikipedia.org/