Intel Pentium M

要谈 2006 年之后的 x86 CPU 发展,就不得不谈 Pentium M 这款特别的处理器,以往 Intel 与 AMD 并没有特别重视笔记型电脑上的 CPU 设计,为了节省研发成本,通常笔记型电脑上使用的行动版处理器就只是同架构桌上型电脑 CPU 降频、降压之后的版本 (LV 版本,Low Voltage),因此在过去好多篇的 CPU 历史中笔者并没有特别著墨于行动版处理器上

Pentium 4-M 的失败

原先在 Pentium 4 这一世代中,Intel 也是循往例推出了同样以 Netburst 架构为基础的 Mobile Pentium 4 (Pentium 4-M),但是很快大家就发现问题了,那就是追求频率最大化优先于 IPC 的 Netburst 并不适合用于对于温度与耗电量有相当大限制的行动运算环境中,将 Pentium 4 降压、降频之后的表现非常不理想,温度比 Pentium III-M 高很多,性能上却没有甚么长进,也没办法用于轻薄笔电之中 (本应对应 Pentium III-M 中的 ULV 版本,到了 Pentium 4-M 时代抑或是性能过差或是根本做不出来)。

而后来由于 Pentium 4-M 近乎凄惨的性能 (而且还很贵),有许多笔记型电脑厂商在旗下的高阶笔电型号 (今天你所见到众多电竞游戏系列的前身) 上乾脆直接选用桌上型电脑版本的 Pentium 4,造就了不少介于桌上型电脑与笔记型电脑之间的四不像出来,至于其他产品线其实 Pentium 4-M 也没能完全取代前代的 Pentium III-M。

Mobile Intel Pentium 4-M (Northwood) 80532

·发布时间:2002 年 04 月 23 日

·运行频率:1400 MHz ~ 3200 MHz

·FSB 频率:400 MT/s、533 MT/s

·L2 缓存大小: 512 KB (全速,On-die)

·支持插槽:Socket 478 ( 478 针脚 FPGA 封装)

·电压需求:1.2 V ~ 1.55 V

·电晶体数:5500 万枚

·制造工艺:0.13 微米 (μm)

·功能:x86-32 + MMX, SSE, SSE2, IST, 部分型号支持 HT

Mobile Intel Pentium 4-M (Prescott) 80546

·发布时间:2004 年 06 月 01 日

·运行频率:2800 MHz ~ 3466 MHz

·FSB 频率:533 MT/s

·L2 缓存大小: 1 MB (全速,On-die)

·支持插槽:Socket 478 ( 478 针脚 FPGA 封装)

·电压需求:1.25 V ~ 1.4 V

·电晶体数:1 亿 2500 万枚

·制造工艺:90 奈米 (nm)

·功能:x86-32 + MMX, SSE, SSE2, IST, HT

救援投手 Pentium M

由于 Intel Pentium 4-M 的失败,Intel 旗下的以色列海法团队 (这团队之后大家还会看到很多次,其辉煌的历史纪录甚至有些人认为只要是海法团队负责的那一代 Intel CPU 就特别有选购的价值) 便开始进行开发后继产品的计划。

以色列海法团队在笔者个人眼中是一个「很敢做对的事」的团队,尽管 Intel 公司当时的主流是 Netbrust 架构,Pentium III 以前使用的 P6 架构早已被认为是「历史产物」,但海法团队认为 Netburst 根本就不适合用于对散热与电压有很大限制的笔记型电脑中,在 Intel Pentium 4-M 的后继产品中选择了海法团队相对而言更熟悉 (海法团队曾经负责同样以 P6 架构为基础的 Timna 处理器,后被取消) 的 P6 架构做为发展的基础,如此「以退为进」的做法,最后得到的产物就是 Pentium M。

「将 Netburst 与 P6 加起来除以二」或许可以贴切的描述 Pentium M 的基础架构,第一代 Pentium M 架构在 Intel 规划上称之为 Banias Micro Architecture (在绝大多数 Intel 文件中不会提到此架构与 P6 老架构之间的关联,因为那很像开倒车跟自打脸 XD),并不单纯只是 Pentium III 架构的复辟,其实 Banias 中融入了不少 Netburst 架构的特色,像是 SSE2 指令集、对分支预测进行强化都是可以在 Netburst 架构上见到的发展方向。

↑ Intel Pentium M (Banias)

Intel Pentium M (Banias) 80535

·发布时间:2003 年 03 月 12 日

·运行频率 (标准电压):1300 MHz ~ 1800 MHz

·运行频率 (低电压):1100 MHz ~ 1300 MHz

·运行频率 (超低电压):900 MHz ~ 1100 MHz

·FSB 频率:400 MT/s

·L1 缓存大小:32 KB 指令缓存、32 KB 资料缓存

·L2 缓存大小:1 MB (全速,On-die)

·支持插槽:Socket 479 ( 478 针脚 FPGA / BGA 封装)

·电压需求 (标准电压):0.956 V ~ 1.484 V

·电压需求 (低电压):0.956 V ~ 1.180 V

·电压需求 (超低电压):0.844 V ~ 1.004 V

·电晶体数:7700 万枚

·制造工艺:130 奈米 (nm)

·功能:x86-32 + MMX, SSE, SSE2, EIST

好一个营销手法:Intel 迅驰移动计算技术

不过 Pentium M 虽然解决了 Intel 在行动版处理器上的问题,却在行销上带来了另一个问题,由于 Netburst 架构已经对消费者灌输了「高频率就是高性能」的观念,但基于改良版 P6 架构的 Pentium M 在频率上几乎都不及 Pentium 4-M,却有著较好的性能,这时候 Intel 若要说服消费者选择新的 Pentium M 岂不是自打脸了吗?其实按照 Intel 官方的说法,Intel 是从此时开始「不再一味追求性能的提升,而是更加强调效能的提升,效能只得是能耗与性能的比值」。

于是为了避免被质疑自打脸,Intel 决定在宣传上淡化 Pentium M 的角色,在宣传上发展了 Centrino 行动运算技术这一套标语政策,再辅以铺天盖地的广告宣传 (当时在台湾连 FM 电台都听得到),让消费者的焦点从处理器上转移到是否具备 Centrino 标章上。

说了这么多,到底 Centrino 到底是什么呢?其实 Centrino 就是 Pentium M 处理器 + Intel 晶片组 + Intel 无线网路卡三位一体的组合搭配,用 Centrino 当宣传让消费者到店里指名购买基于 Centrino 技术的笔记型电脑,不仅可以拉抬 Pentium M 的销售,还连带让自家的无线网路卡销量暴冲,这样的行销策略够聪明吧?所以其实有不少人不认识 Pentium M,却知道 Centrino 这品牌。

·第一代 Centrino (Carmel 平台)

oIntel Pentium M (Banias) 130nm

oIntel 855M 晶片组

oIntel PRO/Wireless 2100BG 无线网路卡

·第二代 Centrino (Sonoma 平台)

oIntel Pentium M (Dothan) 90nm

oIntel 915M 晶片组

oIntel PRO/Wireless 2915ABG 无线网路卡

不再使用频率来命名处理器等级

当今的 Intel 在命名处理器的时候不再使用频率来区分,而是以特殊的处理器编号来命名,例如 i7-5960X,这样的作法其实是从 Pentium M 的第二代产品 Dothan 开始的,同样是为了避免消费者质疑为什么新款处理器的频率比以前还要低而做的做法,从此 Intel 对消费者的「教育」方式转为数字越大的就越高级。

Dothan 基本上就是 Banias 的制程升级版本,从 130 奈米制造工艺升级为 90 奈米制造工艺,FSB 则从 400 MT/s 提升到 533 MT/s 并加入执行禁止位元 (NX bit) 技术。

↑ Intel Pentium M (Dothan)

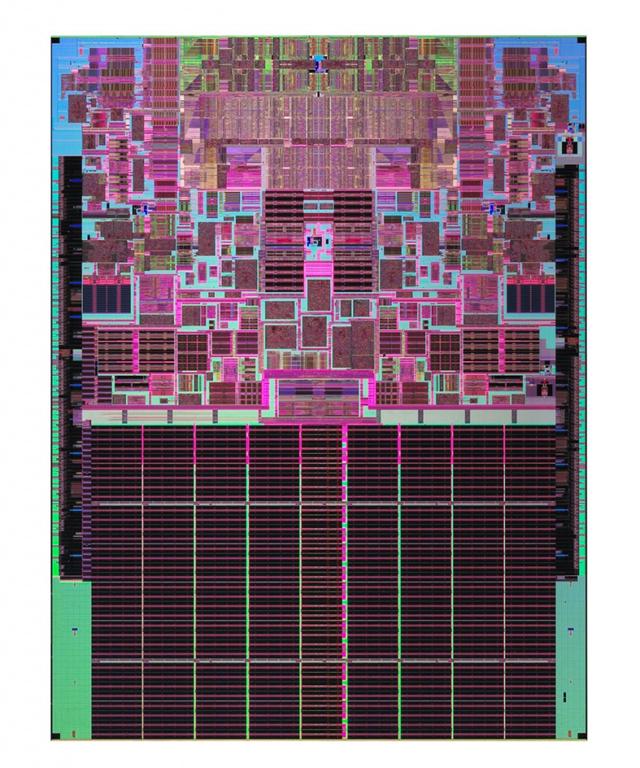

↑ Dothan 的 die shot

Intel Pentium M 700 系列 (Dothan) 80536

·发布时间:2004 年 06 月 23 日

·运行频率 (标准电压):1400 MHz ~ 2277 MHz

·运行频率 (低电压):1400 MHz ~ 1600 MHz

·运行频率 (超低电压):1000 MHz ~ 1300 MHz

·FSB 频率:400 MT/s、533 MT/s

·L1 缓存大小:32 KB 指令缓存、32 KB 资料缓存

·L2 缓存大小:2 MB (全速,On-die)

·支持插槽:Socket 479 ( 478 针脚 FPGA / BGA 封装)

·电压需求 (标准电压):0.988 V ~ 1.404 V

·电压需求 (低电压):0.988 V ~ 1.116 V

·电压需求 (超低电压):0.812 V ~ 0.956 V

·电晶体数:1 亿 4000 万枚

·制造工艺:90 奈米 (nm)

·功能:x86-32 + MMX, SSE, SSE2, EIST, NX

Netburst 殒落,Intel 首次被 AMD 打到趴在地上

很快的 Netburst 终于面临穷途末路,在发展 Prescott 的过程中 Intel 就隐隐约约发现频率是不可能永无止尽的提升下去的,后来的 Tejas 计画也就这么胎死腹中,这段期间应该是 Intel 历史上最灰头土脸的一段,除了 Intel 确定 Prescott 的频率将在 3.8 GHz 止步外,当年度几乎所有 Intel 的主要产品改版通通延期,时任 Intel CEO 的 Craig Barrett 甚至为了 4 GHz 处理器计画的取消与失信于客户而下跪道歉。

同时这也是 Intel 第一次被 AMD 打趴在地上,AMD 的 K8 架构获得了巨大的成功,相较之下 Intel 可说是节节败退,IA-64 失败,x86 架构的 64 位元延伸被 AMD 发展成功、第一颗原生双核心的位置也被 AMD 抢下,Intel 同时期只端出了被戏称为胶水双核心的 Pentium D。

之后 Intel 在 2005 年宣布将在 2006 年推出 Core 架构取代 Netburst。

Pentium M 架构的双核心版本:Yonah

不过 Intel 总不能就这样趴在地上不起来了,Intel 后来在 2006 年 01 月将行动版处理器产品线提升到双核心,也就是开发代号为 Yonah 的 Intel Core 产品线,双核心版本称为 Intel Core Duo,单核心版本则称为 Intel Core Solo,Yonah 是原生双核心设计,单核心版本的 Core Solo 为屏蔽掉一个核心的 Core Duo。

Yonah 整体来说仍是基于 Pentium M 架构进行改良后的产物,新增了 SSE3 指令集,此代产品没有整合 EM64T,因此仍是纯 32 位元 x86 处理器,但此时 Intel 内部正在刮起一场风暴,同时也正在酝酿之后的帝国复兴计划。

Yonah 同时也对应到第三代的 Centrino 平台,代号为 Napa,除了 Yonah 处理器之外还包含了 Intel Pro/Wireless 3945ABG 与 945M 晶片组。

Intel Core (Yonah) 80538/80539

·发布时间:2006 年 01 月 06 日

·运行频率 (标准电压单核心):1400 MHz ~ 2277 MHz

·运行频率 (低电压单核心):1400 MHz ~ 1600 MHz

·运行频率 (标准电压双核心):1600 MHz ~ 2333 MHz

·运行频率 (低电压双核心):1500 MHz ~ 1833 MHz

·运行频率 (超低电压双核心):1200 MHz ~ 1073 MHz

·FSB 频率:533 MT/s、667 MT/s

·L1 缓存大小:2 x 32 KB 指令缓存、2 x 32 KB 资料缓存

·L2 缓存大小:2 MB (全速,On-die,8-way)

·支持插槽:Socket M ( 478 针脚 FPGA / BGA 封装)

·电晶体数:1 亿 5100 万枚

·制造工艺:65 奈米 (nm)

·功能:x86-32 + MMX, SSE, SSE2, EIST, NX, 型号非 50 结尾者支持 VT-x

由于篇幅过长,因此笔者在完稿之后决定将 Intel Core 架构的前世今生分成两篇,这篇是下篇 (Intel Core 架构的逆袭),主要谈 Core 架构本身。

其实笔者等著要写这篇等很久了,2006 年应该是近代 CPU 发展史上最戏剧化的一年,同时也是奠定未来好几年 (至今仍是) 个人电脑世界基础的一年。

从 Intel Core 2 系列开始的 Intel CPU,在规格参数上高低落差很大 (因为共用架构之后型号与产品线差异来自于规格数字的直接调整),因此从本篇开始笔者将不再放上先前几篇文章有的处理器参数介绍。

Intel Core Microarchitecture

笔者要再次强调 2006 这个年份在个人电脑发展史上的重要意义,2006 年同时是 Intel 最惨的一年,却也是奠基后来从 Nehalem、Sandy Bridge、Ivy Bridge、Haswell、Broadwell、Skylake 甚至未来可见的所有 Intel x86 处理器架构基础的 Intel Core 架构诞生的一年,说是帝国复兴、绝地*攻反**其实一点也不为过。

架构回归统一局面

由于相较于 Netburst 架构的失败而言,Pentium M 与 Yonah 架构可说是获得了巨大的成功,因此 2006 年下半推出的 Core 架构再次将行动平台与桌面、服务器平台的 x86 处理器架构统一,整体而言 Core 架构的特性仍然比较接近 Pentium M 与更早期的 P6 架构,因此一般而言我们会认为 Pentium M 就是 Core 架构的前身 (尽管 Intel 官方一再强调 Core 架构是从零打造起的,且融合了 Netburst 与 Pentium M 的架构,不过基本上只是为了给 Netburst 一个比较好的下台阶而已)。

第一款基于 Cre 架构的处理器是 Core 2 Duo,相较于前做 Yonah 而言比较明显的差异是 L2 缓存大小的大幅提升与纳入早已出现在晚期 Netburst 架构产品中出现的 EM64T。

Intel Core 架构主要有三大面向的特性,分别是低耗电、高性能与可扩展性,其中最容易说明且至今仍然适用的是可扩展性这项,因此笔者打算先说明。

可扩展的架构设计

可扩展性可分为两个层次,第一个层次是架构可以适用的范围有多广 (Platform Scalable),以 Core 架构而言,服务器级别的 Woodcrest、个人电脑使用的 Conroe、笔记型电脑使用的 Merom 都是从同样的 Core 架构与同样的 65 纳米制造工艺分化出来的。

↑ Intel Xeon (基于 Core 架构,代号为 Woodcrest) 的 die shot

Intel 开发的时候是先设计出共同的「架构」之后才去分化出不同用途与级别的型号,有需要时 Intel 可以很容易地透过「复制」的方式延展处理器的结构,制造出四核心以上同架构处理器。

第二个层次则是处理器内部结构的模组化设计 (Modular Design),这个特性要等到再下一代的 Nehalem 架构才见得到,因此笔者留待届时再说明。

朝向高效率的设计观点

如同前面所说的,以往 Netburst 架构强调整体性能的提升,因此选择追求拉高频率,尽管因此造成分支预测命中率下降、IPC 性能低落等问题,但在频率的疯涨之下总体的性能仍然是提高的,因此在当时被认为是「好的发展方向」,处理器改良的目的在于极尽所能地提高性能,至于省电与发热量的降低则不是主要考量。

然而这样的设计方针在 Netburst 走到后期时已经被证实并不可行,因为散热装置无法无止尽的延伸下去来承受处理器发热量的不断增长,而且处理器发热量增长的幅度到了后期已经远远超出性能的增加幅度,在无止尽的拉高频率之后性能提升的幅度越来越少,甚至呈现负成长。

因此从 Pentium M 开始,到 Core 架构与现今的 Intel 处理器都朝向提高「效率」的方向前进,强调的是每单位耗能 (瓦) 能带来的性能有多少,效率是能耗与性能的比值,因此除了提高性能很重要之外,降低能耗与发热量也是重点。

Core 架构的新特性

Intel 在宣传 Core 架构时主要强调这五个新特性:

·宽频动态执行技术 (Wide Dynamic Execution)

·智慧型内存存取技术 (Smart Memory Access)

·进阶智慧型缓存 (Advanced Smart Cache)

·进阶数位媒体增强技术 (Advanced Digital Media Boost)

·智慧型电源管理功能 (Intellignet Power Capability)

不过既然是宣传用的,其实这五大点没办法完整说明 Core 架构引入的新特性,所以笔者还是拆开来说明。

宽频动态执行技术 (Wide Dynamic Execution)

宽频动态执行技术 (Wide Dynamic Execution) 其实包含了很多东西,例如接下来介绍的巨集融合技术、比 Pentium M 略多一些的 14 级管线设计 (还是不到 Prescott 夸张的 31 级管线的一半呢)、每个 cycle 可以处理四个指令 (如果有使用到巨集融合则可以是五个) 等,同时 Core 架构的 Simple Decoder 比以往多了一组,分支预测的频宽比 Banias 多了 25%,同时也是 Netburst 的五倍。

巨集融合技术 (Macro-Fusion)

巨集融合是 Intel Core 架构中很重要的一个特性,主要的意思是在指令解码的阶段将特定种类 (不是随便两条指令都可以融合) 的两条连续的 x86 指令合而为一,从而提升指令解码与执行的效率,在此代 Core 架构中只能融合 32 位元指令,因此在 Core 2 系列上有时候可以观察到 32 位元版本程式比 64 位元版本还要快 (除了巨集融合以外另一个原因是 EM64T 只能使用特定几个专属的暂存器)。

尽管巨集融合支持的指令种类相当有限,能融合的情况下也有很多条件要求 (例如必须连续、一个频率周期内只能融合一组、被融合的第一条指令中必须至少用到一个暂存器等),但由于实务上符合条件的情况在编译完成之后的程式中非常常见,因此对性能的提升是可见的 (而且不需要重新编译就能享受到提升),之后历代的 Core 处理器也几乎都会对巨集融合这项功能进行强化,足见这项功能的重要性

进阶智慧型缓存 (Advanced Smart Cache)

其实这项技术说穿了就是两个核心共用一个大的 L2 缓存,从而降低 L2 缓存的失误率 (miss rate),因为以前各自使用专属 L2 缓存的时候经常会发生 Core 1 需要的资料在 Core 2 的 L2 缓存,或是反过来,而这种情况会导致 L2 缓存失误,以致于需要向较慢的内存重新取得资料,而且出现在错误位置的资料反而变成占用该核心所属 L2 缓存,连带也让另一个核心的 L2 缓存失误率拉高。

而且很多时候其实两个核心的负载不会刚好平分,改成共用缓存可以让处理器动态分配,给负载较高或需要较多缓存的核心更多资源 (不论是缓存大小或频宽)。

要注意的是,今日 Intel CPU 的 Smart Cache 其实是指 L3 共用缓存 (以 Skylake 为例,L2 是每个核心各自专属的),但在 Core 2 的时代指的则是 L2。

此外这项设计也给处理器核心之间一个互相沟通的管道,以往两个处理器核心之间是没有连结的,如此造成系统的前端汇流排负担变得非常重 (一次只能接受一个核心使用,再加上一次只能处理一个方向,因此常常会发生排队排到天荒地老的状况),以 Core 2 需要 Core 1 所属 L2 Cache 中的资料为例,得从 Core 2 走 FSB 到主板北桥、内存绕一圈回到 Core 1 的 L2 Cache 才拿得到。

至于在省电方面的帮助则是处理器现在可以关闭暂时没有用到的 L2 部分电路,或是关掉其中一个核心却维持整个 L2 的运行,不像以前是以核心为单位,一次关得全关,有更高的弹性来达到更省电的效果。

进阶数字媒体增强技术 (Advanced Digital Media Boost)

以往受制于实际电路中只设计一组 64 位元的 SSE 运算电路,一个 128-bit 的 SSE 指令会需要两个 cycle 才能完成,Core 架构中的乘法、加法、载入、储存指令都能一次处理 128-bit 长的指令,所以又称为 Single cycle SSE。

智慧型内存存取技术 (Smart Memory Access)

这部分比较难解释,主要是关于 Core 架构降低资料存取延迟对系统性能影响的努力,例如用上 8-Way 的 L1 Cache、16-Way 的超大 L2 缓存等,并放弃了过去 Netburst 架构设计的追踪缓存 (Trace Cache) 设计。

Core 架构中,每个核心有四组预取器 (Prefetcher),其中一组负责预取指令,一组负责预取 L2 缓存,两组负责内存预取,让处理器有能力「学习」最佳的资料存取方式以降低延迟。

另一项重要的功能称为 Memory Disambiguation,透过硬体上实作电路来达到预测后续的指令是否会用到相同的内存位置,从而避免不必要的指令等待,能够提升乱序执行的性能。

首次引入 Tick-Tock 战略规划

众所周知的 Tick-Tock 两年一轮战略规划也是从 2006 年开始的,可以看到后续的 Nehalem、Westmere 都是早在当时就已经确定的规划,至于最下面的 Gesher 后来则改名为 Sandy Bridge。

第二代 Intel Core Microarchitecture (Penryn)

Intel 在 2008 年依照 Tick-Tock 战略规划的预期,推出了称为 Penryn 的新版架构,Penryn 基本上可以认为是 Core 架构的制程升级版,导入新的 45 奈米制造工艺与 High-K 金属闸极技术。

随着制程的不断缩小,漏电流对半导体制成品的影响越来越明显,有越来越高比例的能耗其实是被漏电流「浪费掉」的,因此必然需要做额外的努力来降低漏电流的产生,这就是 High-K 金属闸极技术的目的,同时号称能提高 20% 的电晶体切换速度,可以带来更高的 CPI 与频率。

然而除了制程以外,Penryn 与 Core 在架构上还是有一些不同的,这些不同都是依据 Core 架构强调的五大特性进行更多的强化以求能榨出 Core 架构中潜藏的性能。

主要比较明显的新特性是新加入的 SSE4.1 指令集、更快的前端汇流排 (FSB) 与更大的 L2 缓存 (加大 50%)、速度更快的 Radix-16 除法器,除了这些之外,Intel 表示在虚拟化技术的性能上也有提升。

结语

我想 Intel 在 2006 年发生的事情可以说完美举例了「危机就是转机」、「有心栽花花不开,无心插柳柳成荫」这两句话吧,当年耗费如此多的功夫想发展「全新」的 Netburst 架构,觉得未来会非常顺利的一路向前发展,最后才发现其实当初认为没有办法再走下去而被弃置一旁的 P6 架构才是公司真正的未来,从 P6 架构改良而来的 Core 架构奠下的基础几乎让往后十年 (至今依然如此) 的 Intel 几乎立于不败之地。